經(jīng)過20多年的努力后,,在工藝技術(shù)進(jìn)步和市場需求的推動下,,“大器晚成”的FPGA終于從外圍邏輯應(yīng)用進(jìn)入到信號處理系統(tǒng)核心。在多個(gè)應(yīng)用場合擊敗ASIC后,,現(xiàn)在FPGA廠商又開始將目光瞄向了一向是親密戰(zhàn)友的DSP陣營,。

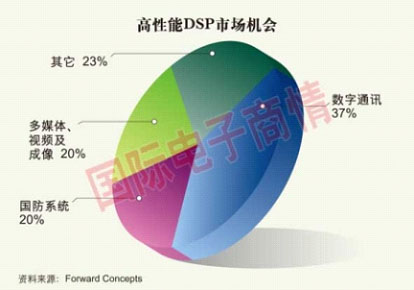

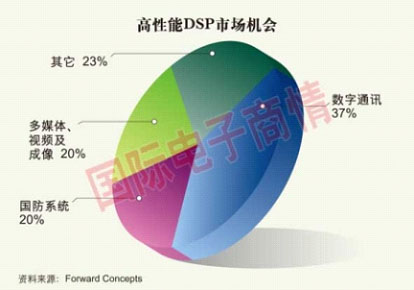

20億美元的新興高性能信號處理市場吸引了眾多供應(yīng)商目光,。

同屬可編程處理平臺,盡管FPGA和DSP芯片供應(yīng)商表面上惺惺相惜,,但面對20億美元的新興高性能信號處理市場,,他們的暗戰(zhàn)已經(jīng)開始。前者將DSP功能從高端FPGA平臺擴(kuò)展到了低成本FPGA,,并加強(qiáng)了相關(guān)開發(fā)工具,,希望在復(fù)雜算法和大量并行處理中補(bǔ)充甚至完全替代DSP,從DSP應(yīng)用中的配角變成主角,;而后者則通過集成ASIC的DSPSoC和多核DSP提升處理能力,,目的也是減少FPGA和ASIC的使用,捍衛(wèi)DSP的主角地位,。此外,,一些初創(chuàng)公司也在開發(fā)并行陣列處理器,宣稱能在單芯片上以相對較低的時(shí)鐘頻率和功耗獲得“前所未有的DSP性能”,。

FPGA渴望“修成正果”

盡管FPGA和DSP一樣擁有20多年的歷史,,但和DSP早早成名相比,F(xiàn)PGA由于成本、功耗和性能限制,,一直在系統(tǒng)外圍暗自發(fā)力,,從初用于膠合邏輯,到用于控制邏輯,,再到用于數(shù)據(jù)通路,,艱難地接近系統(tǒng)核心。傳統(tǒng)上,,F(xiàn)PGA被用作DSP解決方案中所需要的系統(tǒng)邏輯,、多路處理及合并,或是多I/O接口,。

進(jìn)入21世紀(jì)后,,F(xiàn)PGA終于迎來了“修成正果”、與CPU,、DSP并列于系統(tǒng)核心的好機(jī)會:一方面,,隨著90和65納米工藝的采用,F(xiàn)PGA在成本,、功耗和性能上大幅改善,,具備成為系統(tǒng)核心的條件;另一方面,,三網(wǎng)合一(Tri-play)和融合時(shí)代來臨,要求復(fù)雜和大量并行處理,,DSP在做并行處理時(shí)不如FPGA,,這為具有強(qiáng)大并行處理能力的FPGA帶來了需求。

正是因?yàn)槿绱?,?0納米開始,,F(xiàn)PGA巨頭們就爭相推出面向DSP應(yīng)用優(yōu)化的高端FPGA平臺,并在65納米FPGA中進(jìn)一步增強(qiáng)了DSP功能,。例如,,賽靈思面向DSP應(yīng)用的XtremeDSP產(chǎn)品線包括高端的Virtex-4SX和Virtex-5SXT,不久前又推出了低成本Spartan-3ADSP系列,,而Altera的StratixII和StratixIII,,以及65納米低成本CycloneIII系列同樣強(qiáng)調(diào)DSP應(yīng)用。他們的高端FPGA平臺,,瞄準(zhǔn)的是高端通信和視頻應(yīng)用,,如無線基站和包括監(jiān)控、廣播以及3D醫(yī)療圖像在內(nèi)的高分辨率視頻應(yīng)用,;低端平臺則定位于大量對價(jià)格和功耗都很敏感的應(yīng)用,,包括微蜂窩基站、軍用移動軟件定義無線電、超聲系統(tǒng),、輔助駕駛/多媒體系統(tǒng),、高清視頻以及智能IP相機(jī)等——這些也都是傳統(tǒng)DSP芯片看重的新興應(yīng)用。

賽靈思公司中國區(qū)運(yùn)營總經(jīng)理吳曉東強(qiáng)調(diào)說:“為什么會用FPGA做DSP應(yīng)用呢,?DSP表示的是數(shù)字信號處理,,并不代表DSP芯片,實(shí)際上數(shù)字信號處理有很多不同實(shí)現(xiàn)方法,,可以用DSP芯片,,也可以是MCU,還可以是FPGA和ASIC作數(shù)字信號處理,。事實(shí)上,,由于FPGA是一個(gè)天生的并行處理結(jié)構(gòu),因此在進(jìn)行復(fù)雜計(jì)算時(shí)性能遠(yuǎn)遠(yuǎn)超過傳統(tǒng)DSP芯片,。”

賽靈思亞太區(qū)市場營銷董事鄭馨南表示,,過去20年里算法復(fù)雜性快速提升是推動FPGA進(jìn)入DSP應(yīng)用的重要市場動力。他以通信領(lǐng)域?yàn)槔仡橠SP應(yīng)用歷史說,,20世紀(jì)70年代,,DSP應(yīng)用的驅(qū)動力為語音頻帶,性能需求的數(shù)量級為“KHz”,,微處理器和MCU可以滿足需求,;20世紀(jì)80、90年代,,無線電為DSP應(yīng)用驅(qū)動力,,性能需求為“MHz”級,DSP獨(dú)領(lǐng)風(fēng)騷,;而進(jìn)入21世紀(jì),,三網(wǎng)合一(Tri-play)要求非常復(fù)雜的處理,只有DSP+FPGA才能夠滿足需求,。

吳曉東進(jìn)一步解釋說,,傳統(tǒng)DSP芯片是實(shí)時(shí)信號處理的佳答案,但它畢竟是一個(gè)串行結(jié)構(gòu),,進(jìn)行復(fù)雜運(yùn)算時(shí)可能來回循環(huán)幾百次,,因此速度反而不是很快,單個(gè)DSP處理器很難滿足5GMACS以上性能需求,;而FPGA是天生的并行處理結(jié)構(gòu),,包含了幾百個(gè)MAC單元,因此性能遠(yuǎn)遠(yuǎn)高于傳統(tǒng)DSP芯片,,例如我們的Virtex-5SXTFPGA在550MHz下性能可達(dá)550MSPS,;而主頻為1GHz的DSP性能只能達(dá)到8MSPS。他總結(jié)說:“由于FPGA可以彌補(bǔ)DSP芯片的不足,在信號處理系統(tǒng)中FPGA與DSP相得益彰,。”他一再強(qiáng)調(diào)FPGA不是要與DSP直接競爭,,“我們現(xiàn)在更多的還是互補(bǔ)的關(guān)系。”

他舉例說,,以前視頻監(jiān)控應(yīng)用的通道數(shù)不多,,對圖像質(zhì)量和實(shí)時(shí)性等也要求不高,很少有人用FPGA,;但是隨著監(jiān)控由標(biāo)清轉(zhuǎn)向高清,,從單通道轉(zhuǎn)到八通道,從非實(shí)時(shí)轉(zhuǎn)到對實(shí)時(shí)的要求,,外加人臉識別和運(yùn)動估計(jì)等分析功能,,普通DSP就很難實(shí)現(xiàn),需要多片DSP來一起處理,,成本十分昂貴,。而用DSP+FPGA的方式則十分完美,可以大大節(jié)省成本,。其中,,F(xiàn)PGA用于加速實(shí)時(shí)視頻處理和壓縮,而DSP運(yùn)行實(shí)時(shí)操作系統(tǒng)和第三方分析軟件,。

對于另一個(gè)目前的大熱市場,,3G和WiMAX基站,他則表示可利用FPGA的并行處理能力來設(shè)計(jì)數(shù)字上下變頻器,,因?yàn)閷τ谛枰噍d波的數(shù)字變頻器,,并行的FPGA是好地選擇;而DSP則適合于變頻后的符號率處理,。

但是,DSP廠商絕不會只滿足于僅做后端的符號處理,,比如TI早就推出針對數(shù)字上下變頻的產(chǎn)品,。

另一邊,賽靈思實(shí)際上也并不滿足于協(xié)處理器的位置,。在其代理商安富利前不久舉辦的“安富利與賽靈思技術(shù)研討會”上,,安富利展示的一些視頻應(yīng)用已完全將FPGA作為主芯片,并不是協(xié)處理器來使用,。作為賽靈思主要的方案推廣商,,這也暗示了FPGA未來要走的路。

DSP陣營捍衛(wèi)主角地位

對于來自戰(zhàn)友的挑戰(zhàn),,DSP廠商正在通過集成ASIC+DSP的SoC(系統(tǒng)級芯片)和多核DSP提升處理能力,,目的也是減少FPGA和ASIC的使用,捍衛(wèi)自己的主角地位。

對于FPGA作為協(xié)處理器的觀點(diǎn),,TI中國區(qū)通用DSP業(yè)務(wù)拓展經(jīng)理鄭小龍也表示認(rèn)同,,他指出:“在需要高級別并行處理的情況下FPGA是一種選擇,也是FPGA適合的場合,。在高性能和多通道應(yīng)用中采用DSP+FPGA往往更能勝任,,而不是單獨(dú)采用其中某一種平臺。有了可編程DSP,,大多系統(tǒng)控制,、排序化處理、用戶功能化和信號處理可在DSP上運(yùn)行,。如果要加快并行處理,,采用FPGA就理所當(dāng)然。”

但鄭小龍同時(shí)指出,,當(dāng)某個(gè)應(yīng)用中FPGA實(shí)現(xiàn)的并行加速處理達(dá)到一定市場規(guī)模而足以進(jìn)行專用集成時(shí),,TI會將硬件加速器集成到DSP中去,這樣可以比外掛FPGA在獲得同樣性能的前提下價(jià)格和功耗保持在一個(gè)較低的水平,。他解釋說:“雖然FPGA能提高信號處理鏈路的速度,,但隨著技術(shù)成熟,這些功能可以以較低成本集成到DSP處理器中,,比外加一個(gè)芯片效率更高,。因此,對于那些特定應(yīng)用,,DSP將提供更優(yōu)異的解決方案,。

另外,TI還通過多核DSP提升性能,。一個(gè)典型的例子就是,,TI不久前針對WCDMA基站推出了高集成度的TCI6?88,它采用3個(gè)1GHzDSP核,,能夠在單芯片上支持宏基站所需的所有基帶功能,,無需FPGA、ASIC及其它橋接器件,。這是因?yàn)門CI6?88中已經(jīng)包含了WCDMA系統(tǒng)處理所需的專用協(xié)處理器,,例如傳統(tǒng)DSP中沒有的Viterbi(VCP2)與Turbo(TCP2)協(xié)處理器——過去它們或采用FPGA/ASIC來實(shí)現(xiàn),或要靠DSP核來解決,,這就需要增加額外的DSP,。TCI6?88還具有典型DSP所沒有的多種外設(shè),如新興的高速天線接口OBSAI/CPRI,,而其它沒有這種接口的器件必須采用一個(gè)FPGA或ASIC管理協(xié)議轉(zhuǎn)換,。此外,,如果一個(gè)系統(tǒng)需要規(guī)模擴(kuò)展到去支持更多的用戶,TCI6?88還可以通過采用RapidIO接口或者外設(shè)去實(shí)現(xiàn)互連,。鄭小龍總結(jié)說:“TCI6?88是一個(gè)三核DSP,,它具有很大的處理能力去支持多種多樣的基帶處理,無需ASIC/FPGA參與,。”

他還強(qiáng)調(diào)說,,單核DSP同樣可以取代DSP+FPGA/ASIC方案,只是單核DSPSOC只可以支持有限數(shù)量的用戶,,而多核DSP則能夠支持更多用戶和更多功能,。鄭小龍指出:“只要DPS具有恰當(dāng)?shù)耐庠O(shè)、協(xié)處理器和處理速度(MIPS)去有效實(shí)現(xiàn)所需的功能,,它就可以成為SoC,。在一些情況下,處理需求受到現(xiàn)行技術(shù)的限制,,就必須考慮多核,,例如TCI6?88具有總計(jì)3GHz性能來滿足指定需求,而單個(gè)的3GHz核在當(dāng)今還不能實(shí)現(xiàn),,所以就要采用多核,。”

其實(shí),吳曉東也坦承FPGA和DSP雖然不是替代關(guān)系,,但也存在一定的競爭關(guān)系,,尤其是Spartan-3ADSP這種低成本FPGA開始覆蓋更廣闊的DSP應(yīng)用(1-30GMACS性能范圍),與DSP的競爭難免,。他表示:“目前趨勢是一個(gè)往下走(FPGA),,一個(gè)往上走(DSP),雙方都為了彌補(bǔ)性能上的鴻溝,,都是為了更好滿足市場需求,,終的抉擇取決于客戶和應(yīng)用。”吳曉東指出,,很難為客戶選擇DSP還是FPGA劃定一個(gè)明顯的界限,,目前看來5GMACS以下普通DSP容易實(shí)現(xiàn),5GMACS以上可能就需要多片DSP去處理,,這時(shí)候FPGA更有優(yōu)勢。

而作為信號處理的傳統(tǒng)主導(dǎo)者,,TI則認(rèn)為未來DSP將繼續(xù)是用戶的,。鄭小龍表示,高速數(shù)字信號實(shí)時(shí)處理是DSP和FPGA所共同面對的應(yīng)用,,兩者都屬于可編程處理平臺,,但實(shí)現(xiàn)的方法卻大相徑庭,,DSP采用軟件編程,而FPGA則借助硬件編程手段,。當(dāng)一個(gè)軟件可編程DSP被用于承擔(dān)任何一種處理負(fù)載時(shí),,它就可以成為優(yōu)選的平臺,因?yàn)橄啾绕渌幚砥?,DSP可以在較低的成本下同時(shí)具有好的性能和功耗,。他強(qiáng)調(diào)說:“通過在DSP平臺上持續(xù)發(fā)展多種多樣的外設(shè)、嵌入式軟件,、加速器和協(xié)處理器,,TIDSP將持續(xù)保持作為今天和未來實(shí)時(shí)應(yīng)用中優(yōu)選系統(tǒng)構(gòu)架的地位。”

但是,,吳曉東也表示,,他們通過將XtremeDSP核固化后,可以將功耗大大降低,,且在實(shí)現(xiàn)MAC功能時(shí),,比DSP具有更低的成本。比如通過Spartan-3A可實(shí)現(xiàn)性能超過20GMACS,,但成本不到30美元的方案,。

高性能DSP處理器未來的發(fā)展方向

在TI看來,多核和SoC是高性能DSP未來的發(fā)展方向,。鄭小龍介紹說,,TI對高性能DSP的展望包括增強(qiáng)靈活的協(xié)處理器,與單核或多核DSP協(xié)作,。這些下一代的DSP將整合許多現(xiàn)在所使用的ASIC類型功能,,還將支持更多特性和性能,并有能力運(yùn)行在更高速度以支持更多的數(shù)據(jù)吞吐量,。通過性能提升,,DSP在目前采用CPU或ASIC的應(yīng)用領(lǐng)域中更有優(yōu)勢——部分地取代任何一種。事實(shí)上,,在大眾市場上,,TI已經(jīng)有DSP和CPU相結(jié)合的產(chǎn)品推上市場,也就是已經(jīng)量產(chǎn)的“達(dá)芬奇(DavVinci)”系列產(chǎn)品,。

在多核DSP方面,,目前的TI多核產(chǎn)品設(shè)計(jì)為滿足不同細(xì)分市場的不同需求。TCI6?88目標(biāo)是無線基站處理市場,;TNETV3020針對有線網(wǎng)絡(luò)的高密度語音市場,。前者采用3個(gè)1GHzDSP核,后者則采用了6個(gè)500MHzDSP核,。

不過與TI,、飛思卡爾等廠商的多核DSP策略有所不同的是,,許多初創(chuàng)公司正在開發(fā)并行陣列處理器芯片,宣稱能在單一芯片上以相對較低的時(shí)鐘頻率和功耗獲得“前所未有的DSP性能”,。

例如,,新興基站芯片廠商PicoChip的多核DSP——picoArray處理器是一種粗粒度的超大規(guī)模并行異構(gòu)16位處理器陣列,其運(yùn)算和通信資源是靜態(tài)分配的,。它含有322個(gè)處理單元,,在160MHz的主頻下能提供200GMIPS和40GMACS的性能,據(jù)稱性價(jià)比或功率/性能比至少是其它架構(gòu)(無論是DSP還是FPGA)的10倍,,可取代含有多個(gè)DSP,、FPGA及通用控制器的混合架構(gòu)體系,適用于3G/4G和WiMax基站,,并且能夠?qū)崿F(xiàn)“軟件無線電”,。

但TI表示,這種如此龐大的并行架構(gòu)應(yīng)用非常有限,,而且存在固有缺陷,,因此TI沒有去開發(fā)這種產(chǎn)品。鄭小龍解釋說:“將數(shù)以百計(jì)的DSP核放到一個(gè)芯片上完全可能,,TI目前并沒有追求這種類型的大規(guī)模并行架構(gòu),,其原因在于這種產(chǎn)品的局限性。例如一個(gè)客戶所需要運(yùn)行的應(yīng)用必須有益于這樣一種架構(gòu),,而由集成上百個(gè)DSP所帶來的固有挑戰(zhàn)在于三個(gè)方面,,一是存儲器的局限性,如此多的核要有效運(yùn)行就需要一個(gè)相當(dāng)大的數(shù)據(jù)和程序存儲器,;二是當(dāng)上百個(gè)核都要去訪問數(shù)據(jù)時(shí),,提供平等的訪問去共享如外設(shè)、板上和外部存儲器將很困難,;三是在器件中有更多的核就會有更多的互連,,這將增加阻塞。”

其實(shí),,這些新興處理器廠商面臨的更嚴(yán)重問題是缺乏像DSP和FPGA這樣完善的軟件工具支持,,這才是新興處理器廠商進(jìn)入市場致命的挑戰(zhàn)。

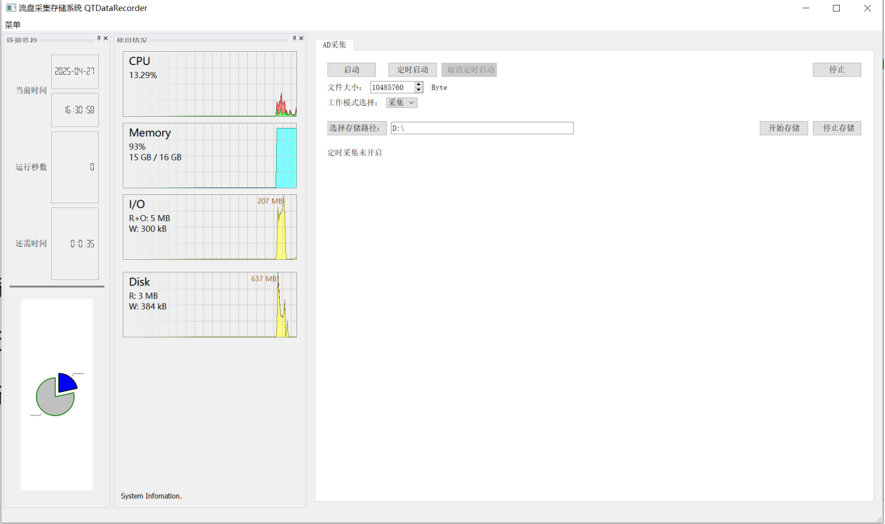

關(guān)于坤馳科技:

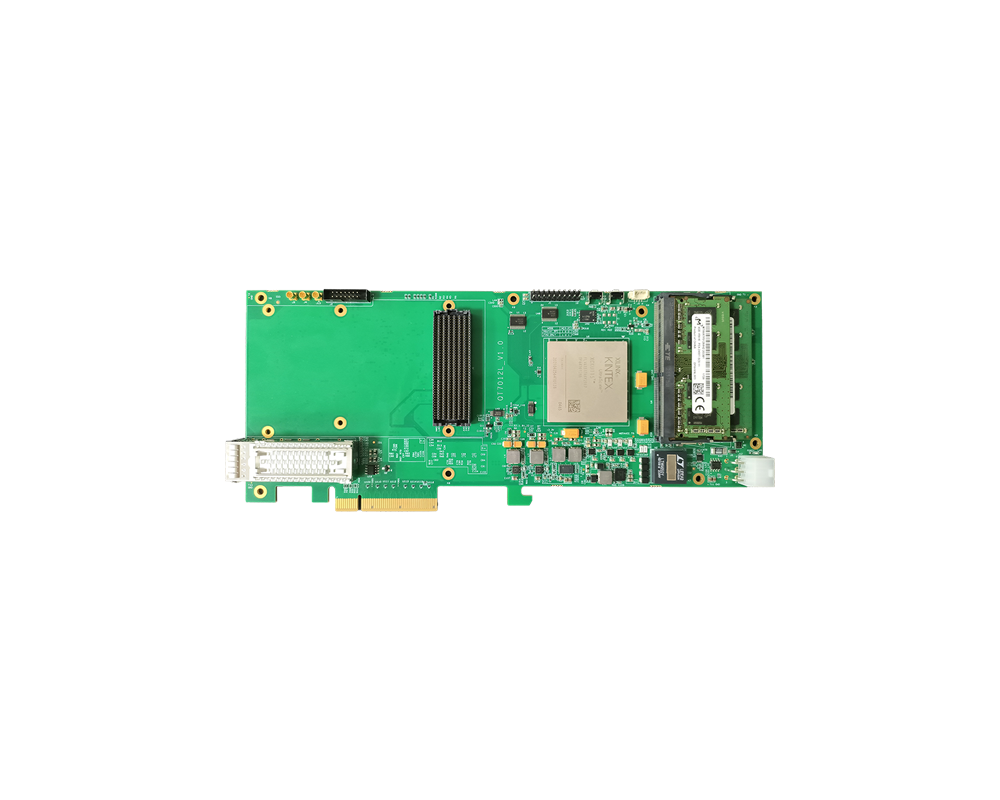

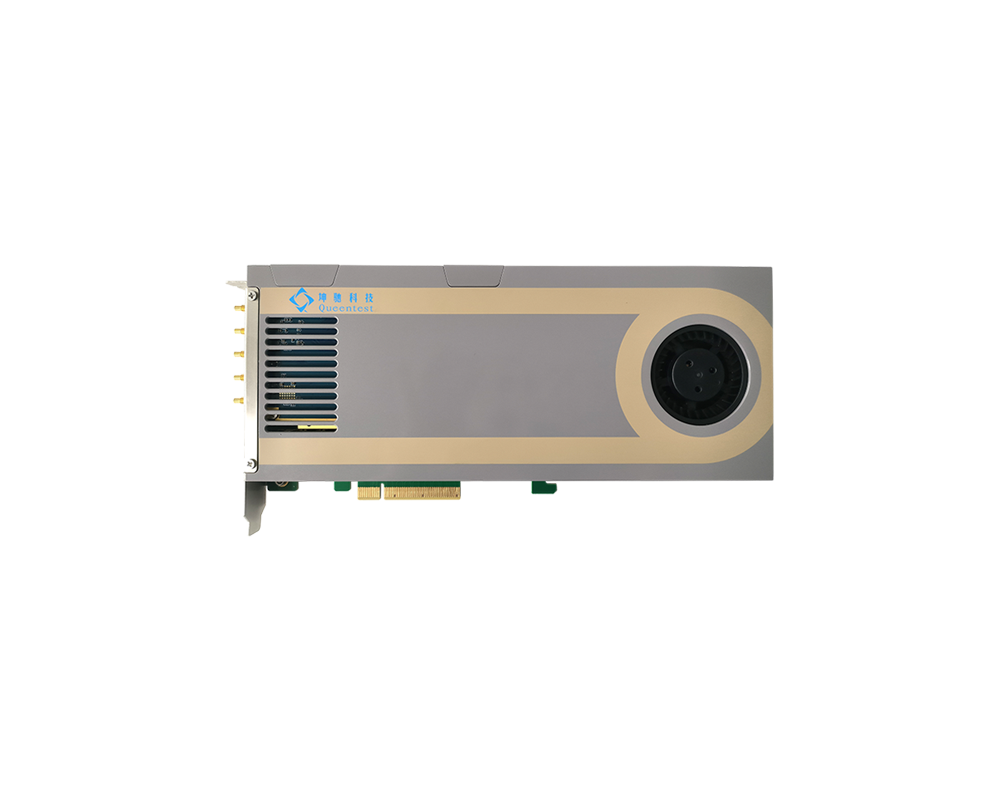

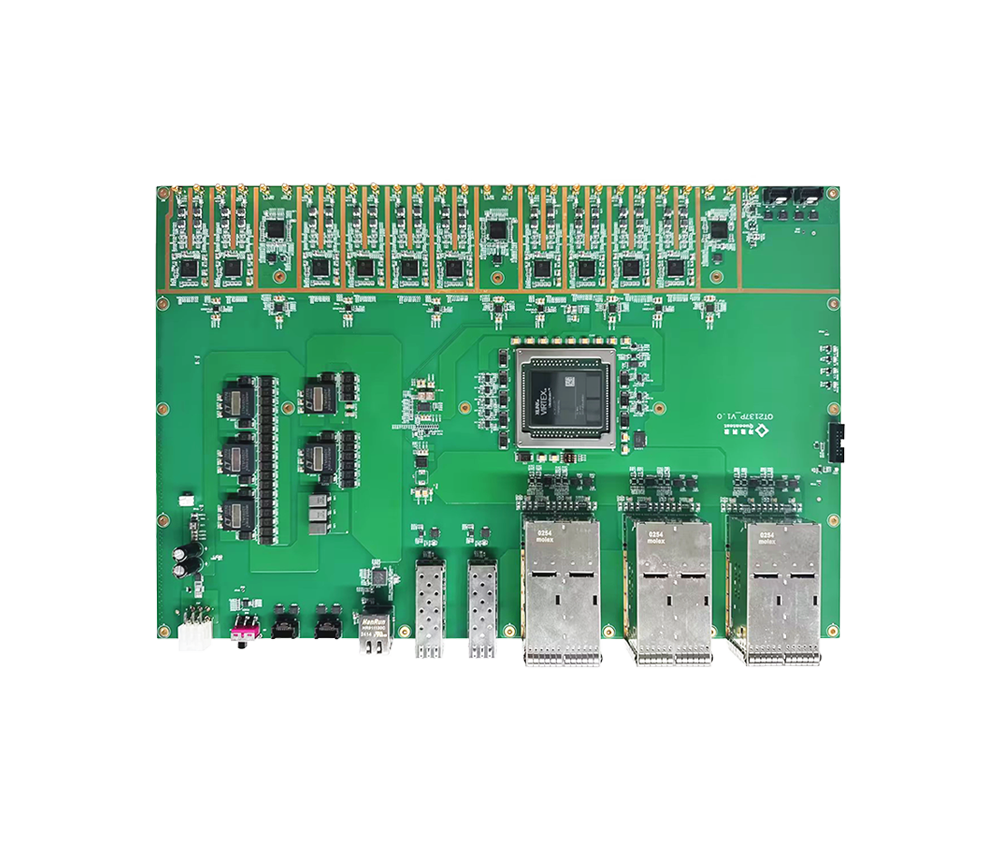

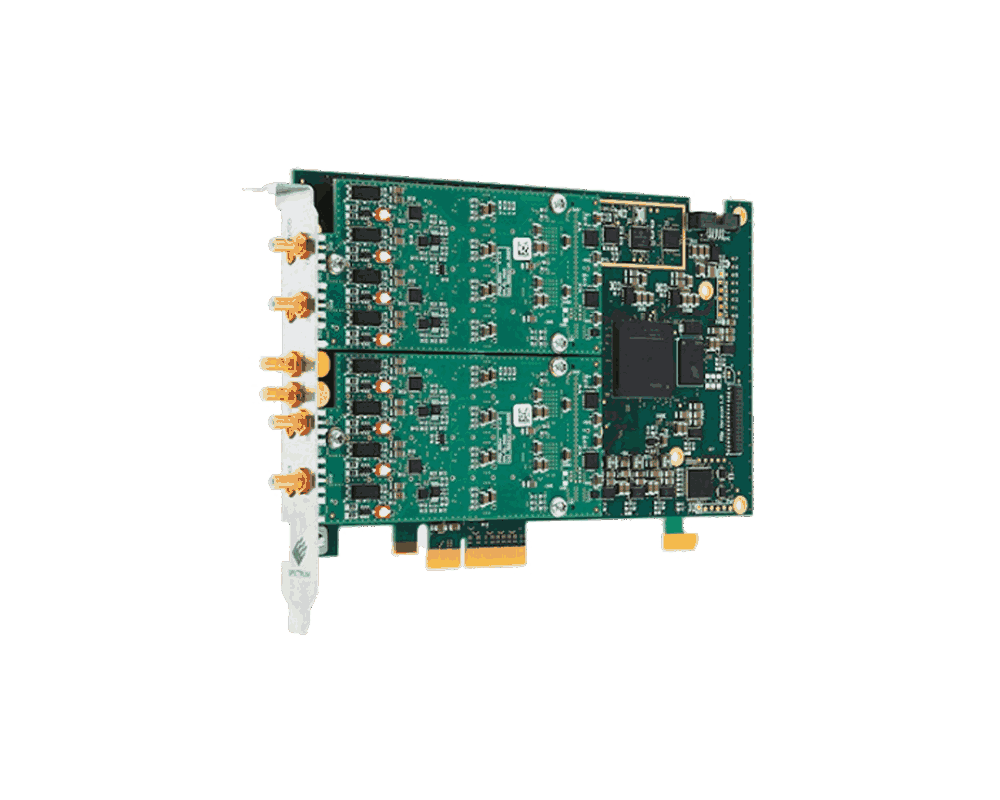

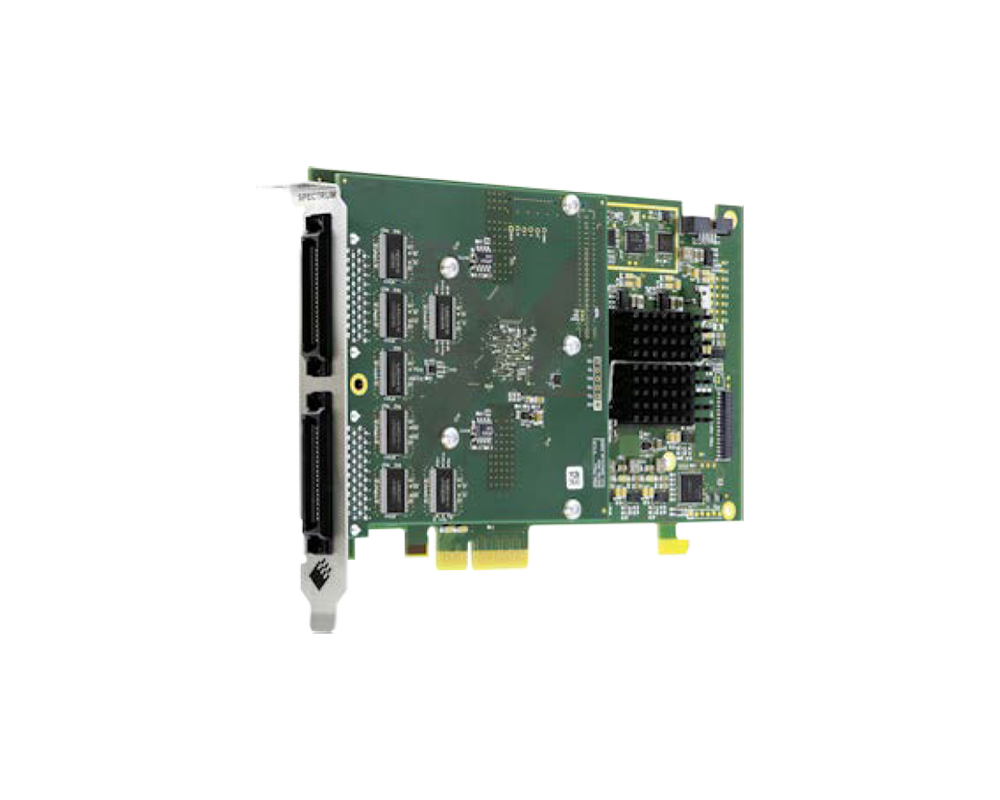

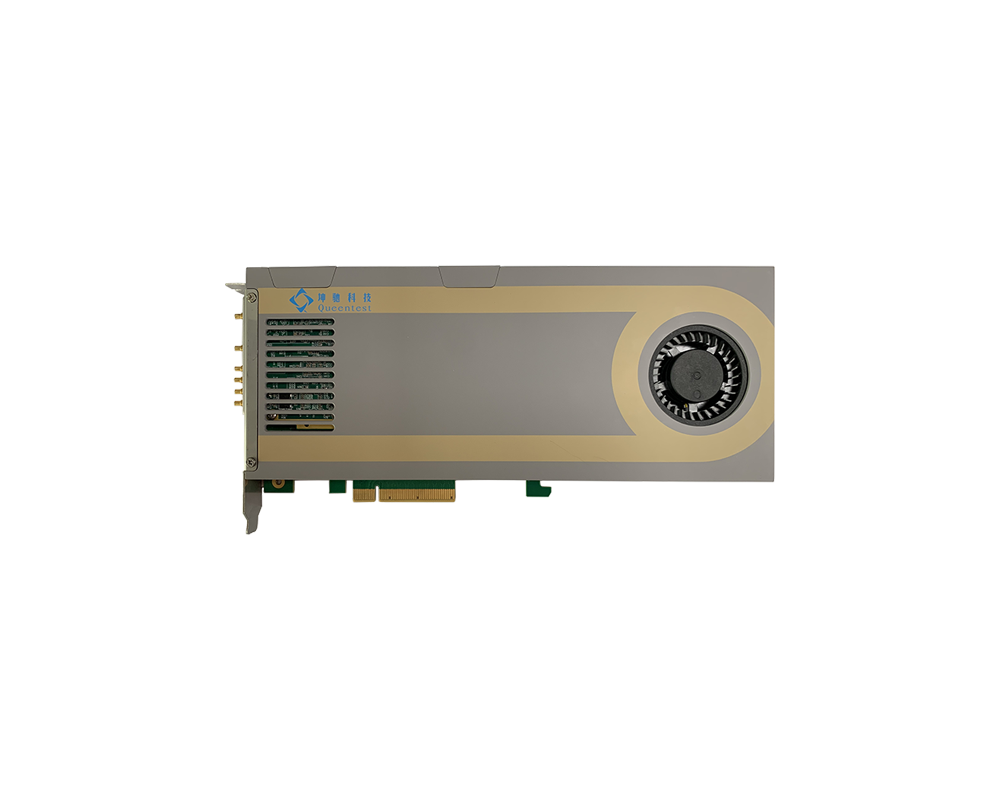

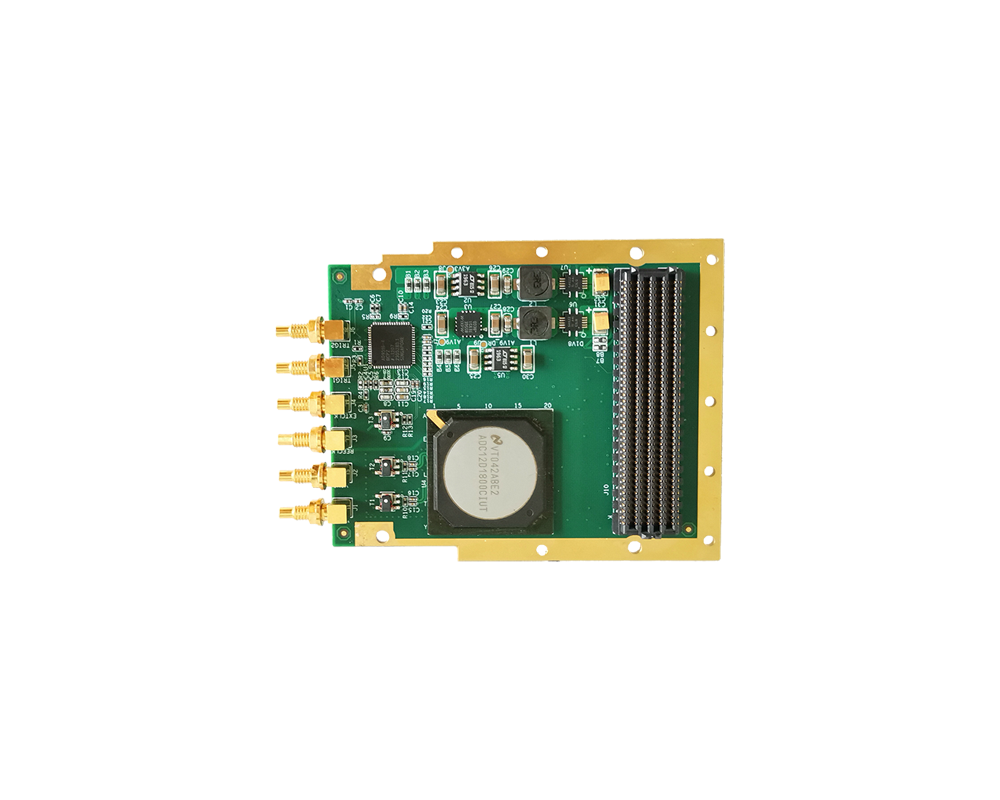

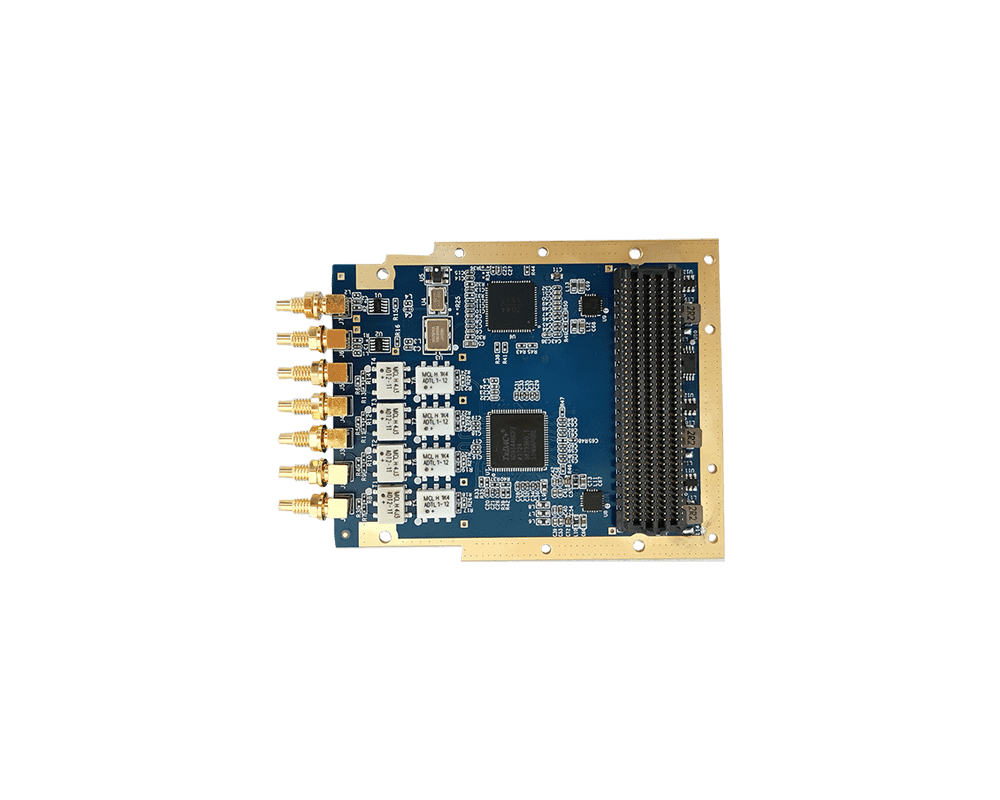

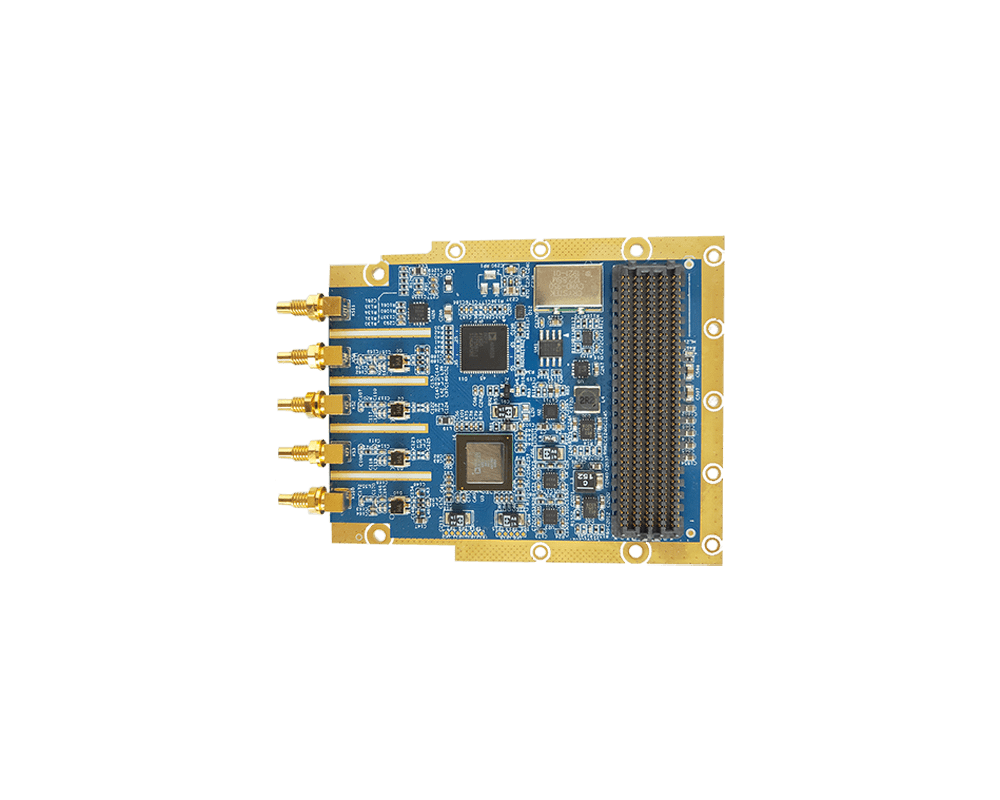

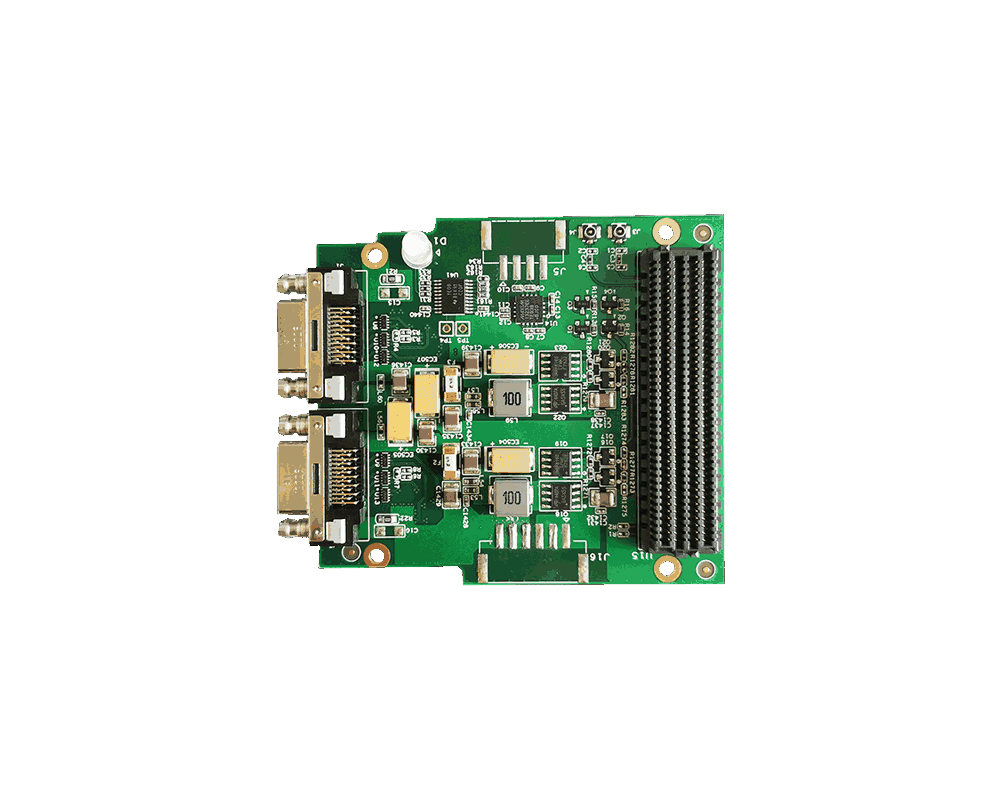

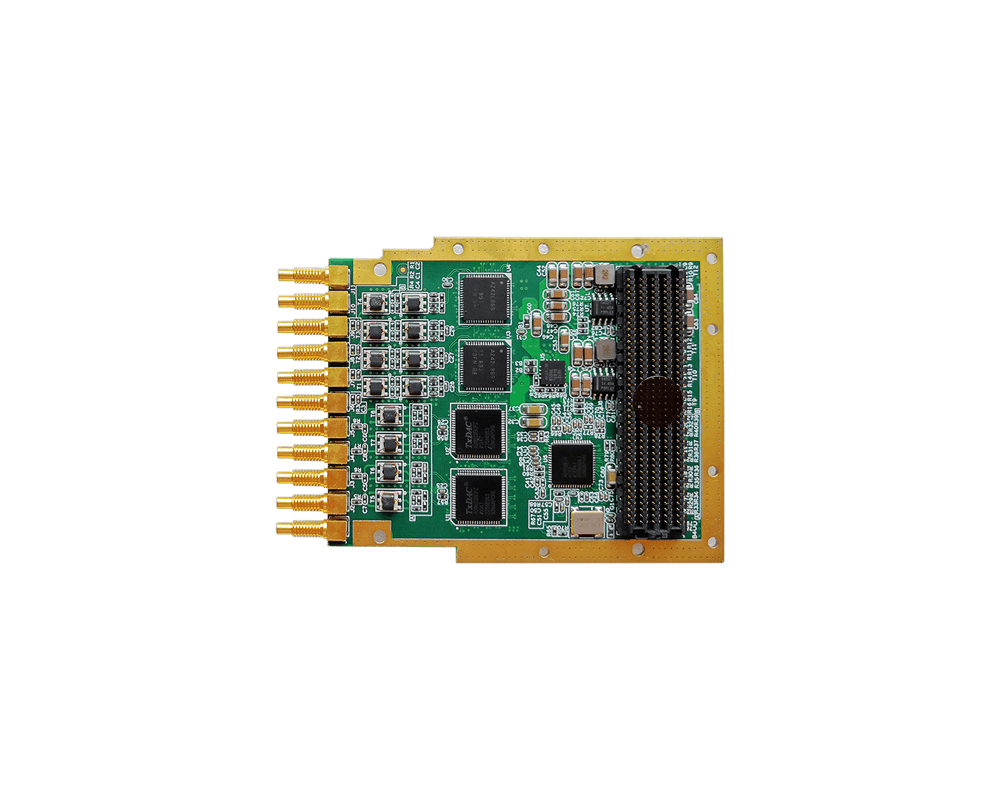

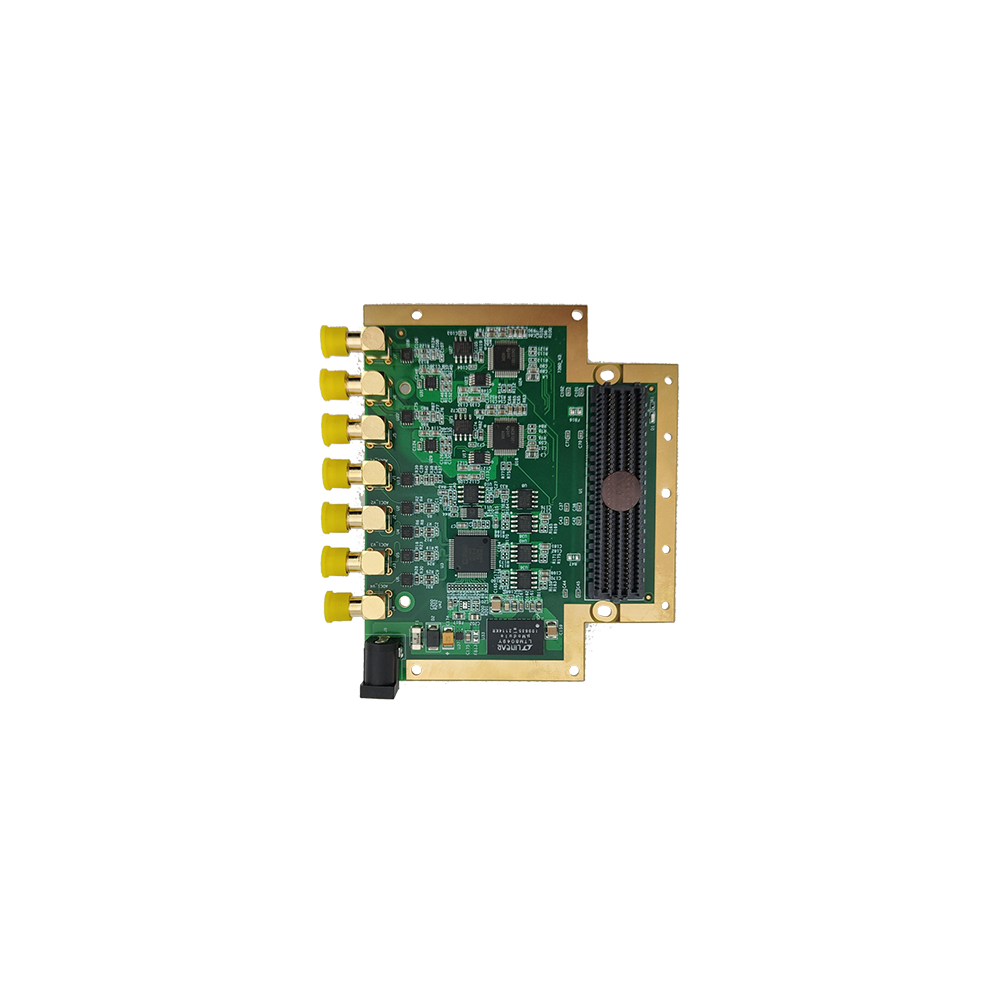

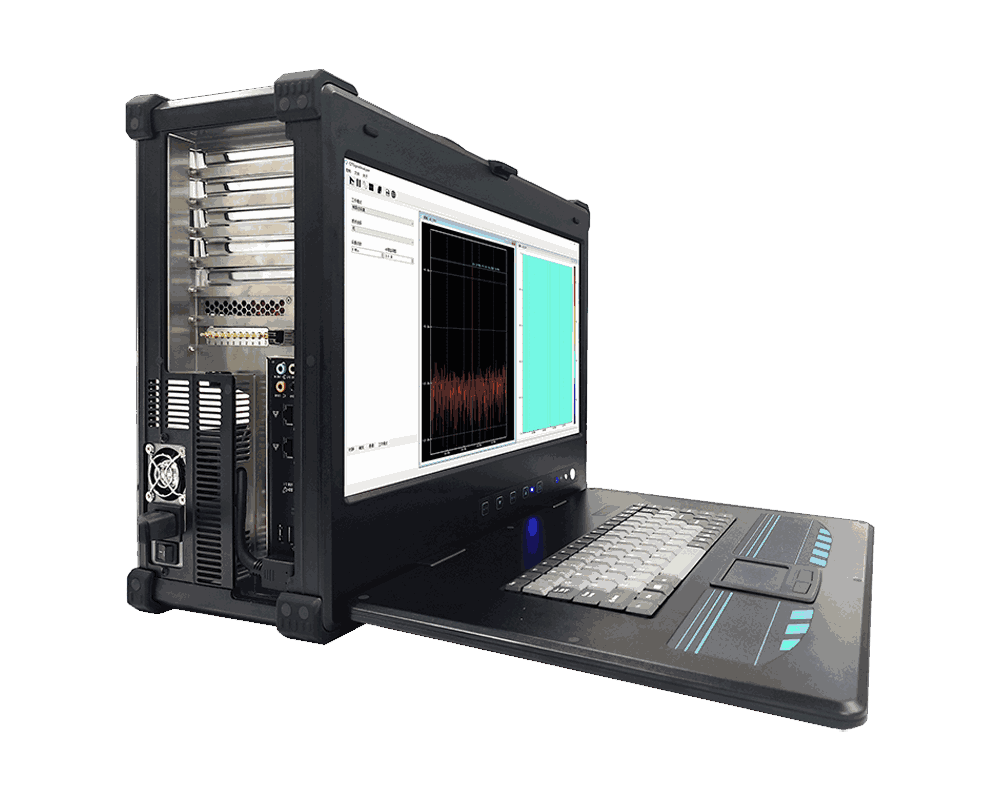

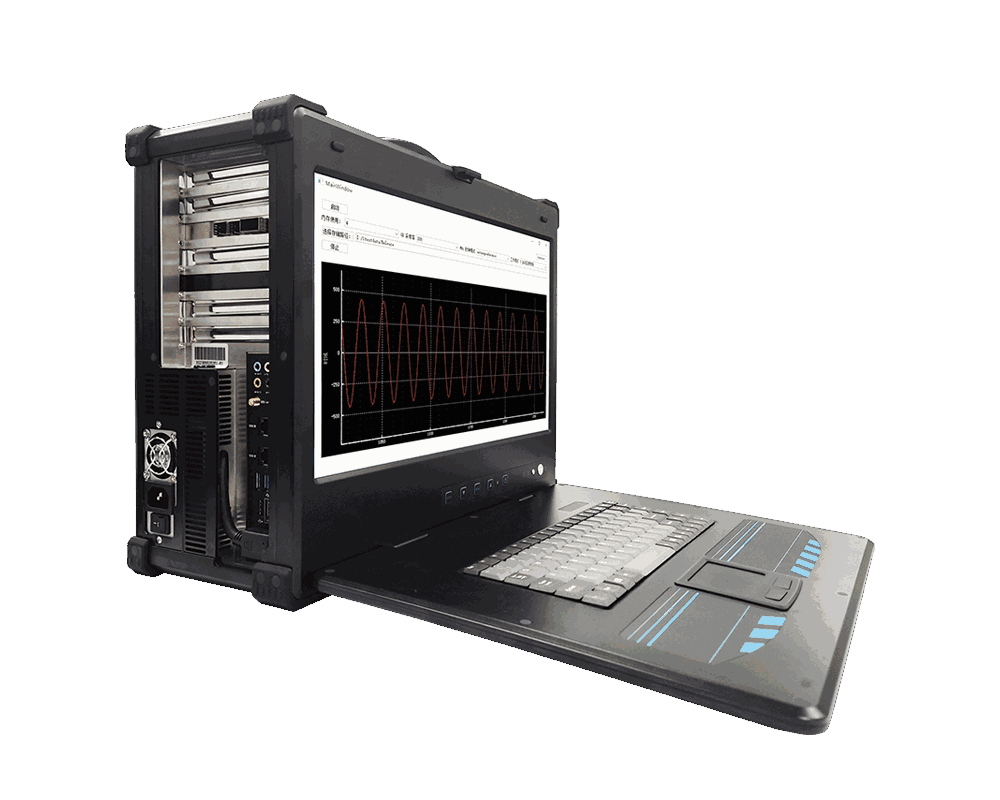

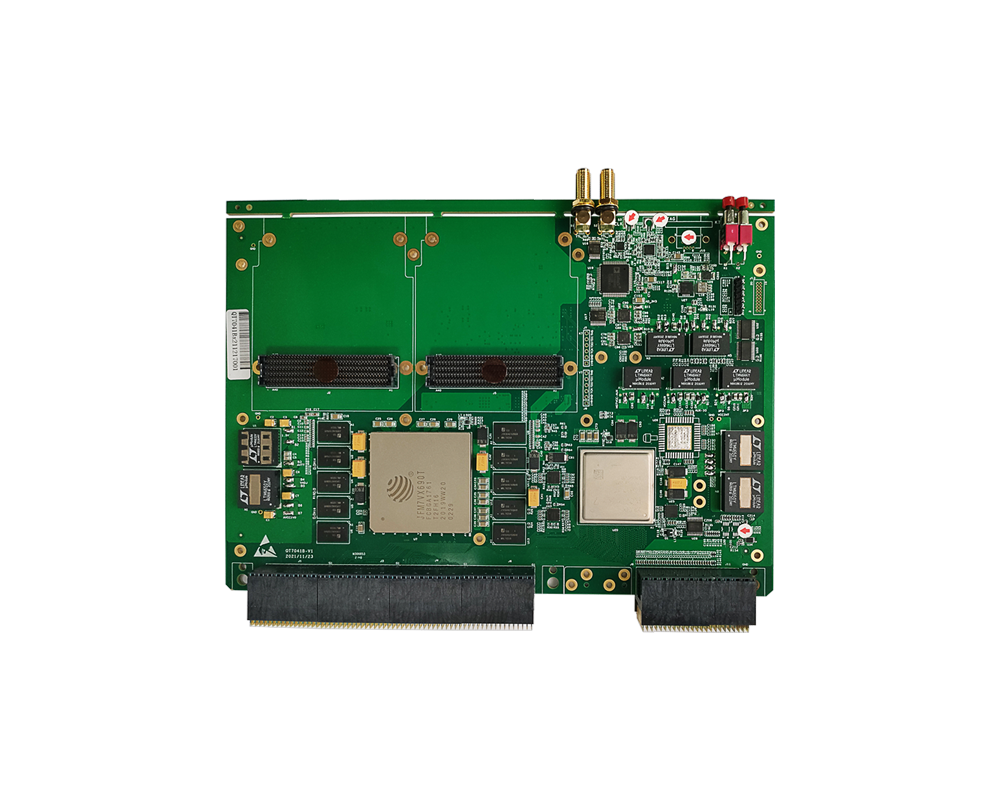

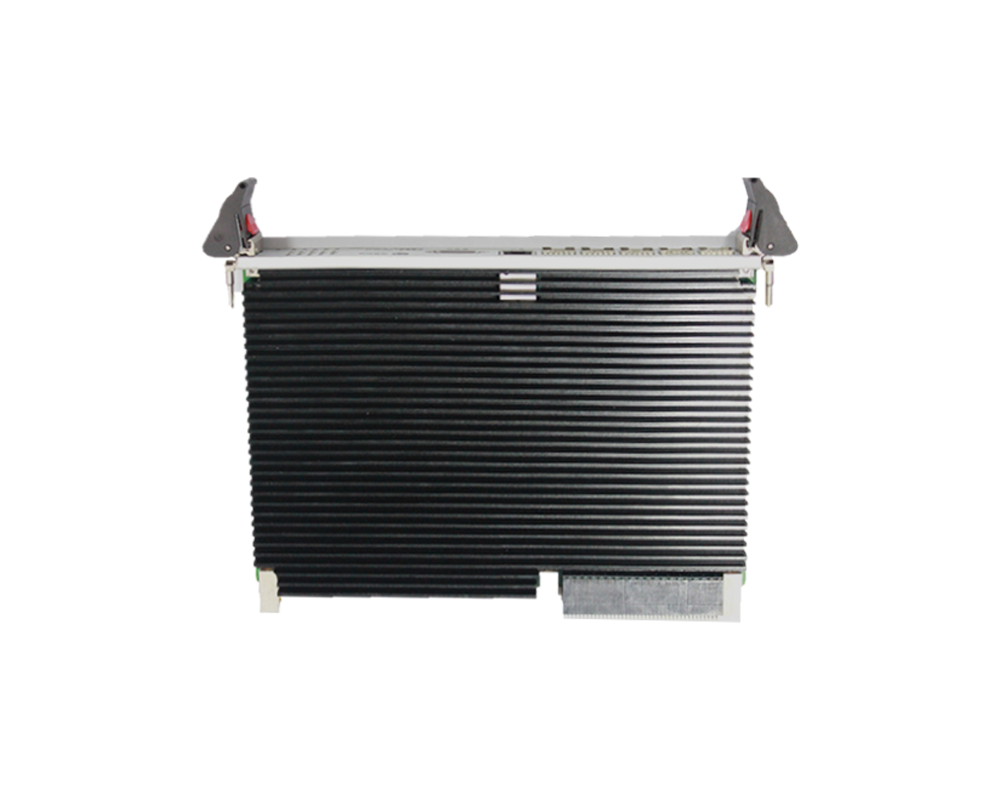

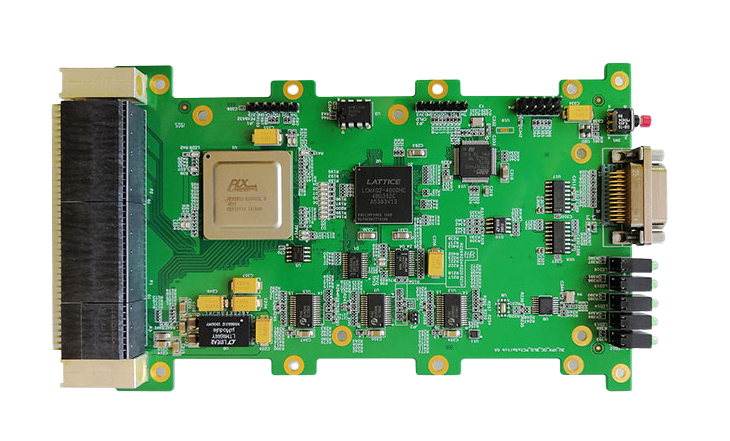

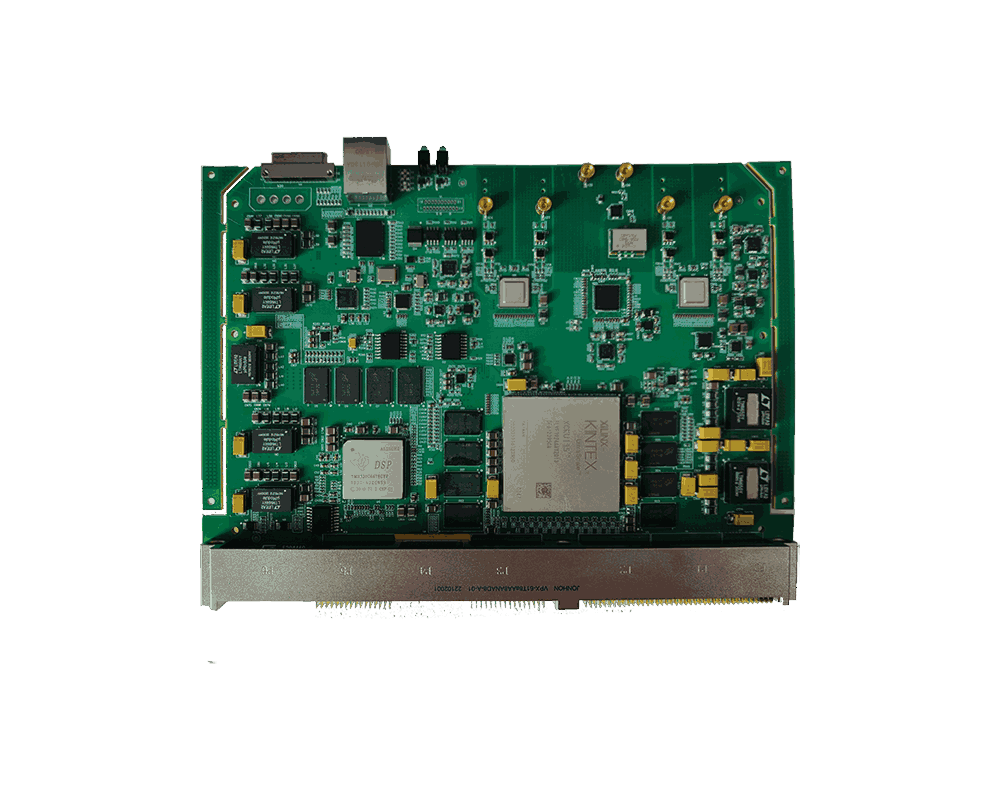

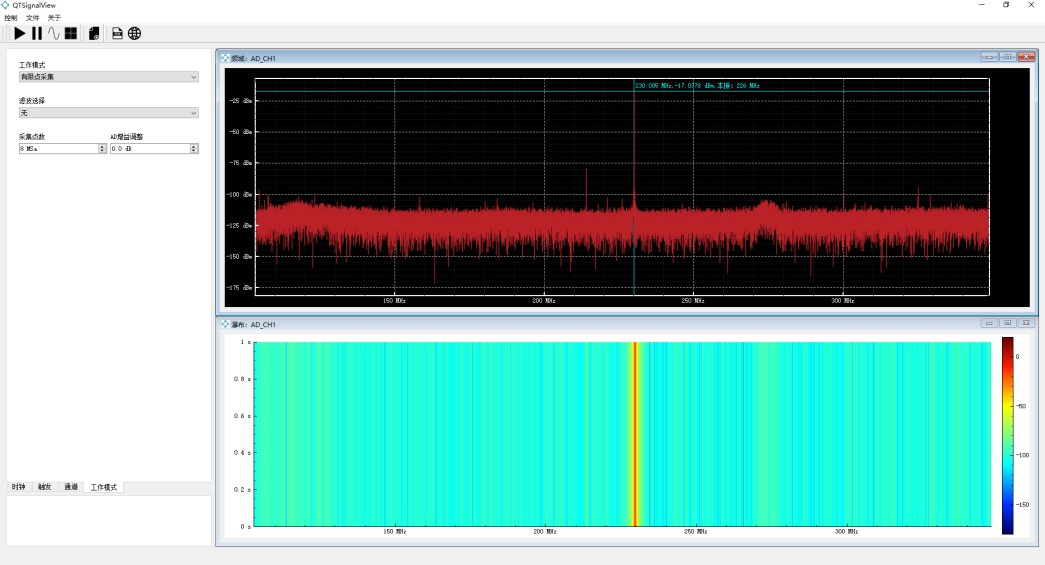

坤馳科技是專注于高速數(shù)據(jù)采集與信號處理,、高速數(shù)據(jù)存儲與記錄的高科技公司,。坤馳科技為用戶提供成熟的標(biāo)準(zhǔn)高速數(shù)據(jù)采集產(chǎn)品與技術(shù),也可為用戶提供定制化的高速信號采集解決方案,。目前坤馳科技服務(wù)過的研究所,、科研單位已達(dá)近百家。高速數(shù)據(jù)采集產(chǎn)品線涵蓋PCIExpress,、cPCI,、PXIe、VPX,、USB等總線,,包含高速AD、DA平臺,、FPGA,、DSP處理平臺,SATA/SSD,、Flash存儲平臺等,。

全國咨詢電話:400-000-4026

公司官方網(wǎng)站:http://m.jtyykv.cn

官方微博:http://e.weibo.com/queentest

官方微信:queentest或掃描: