- 方案概述

- 相關產(chǎn)品

- 聯(lián)系我們

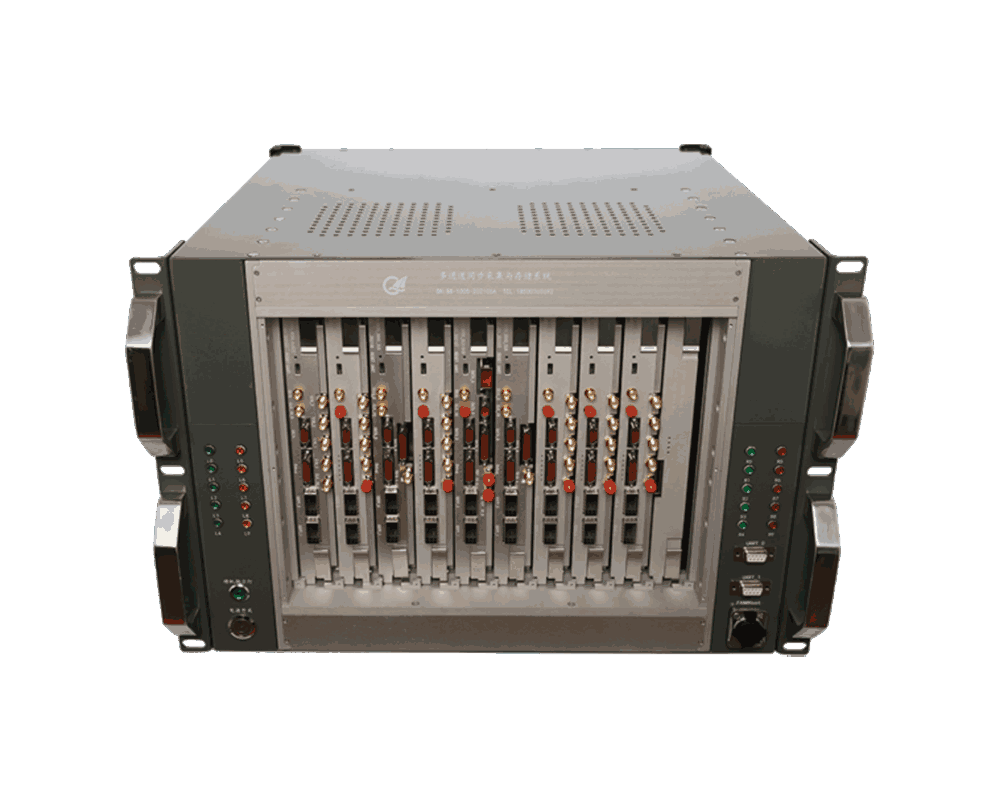

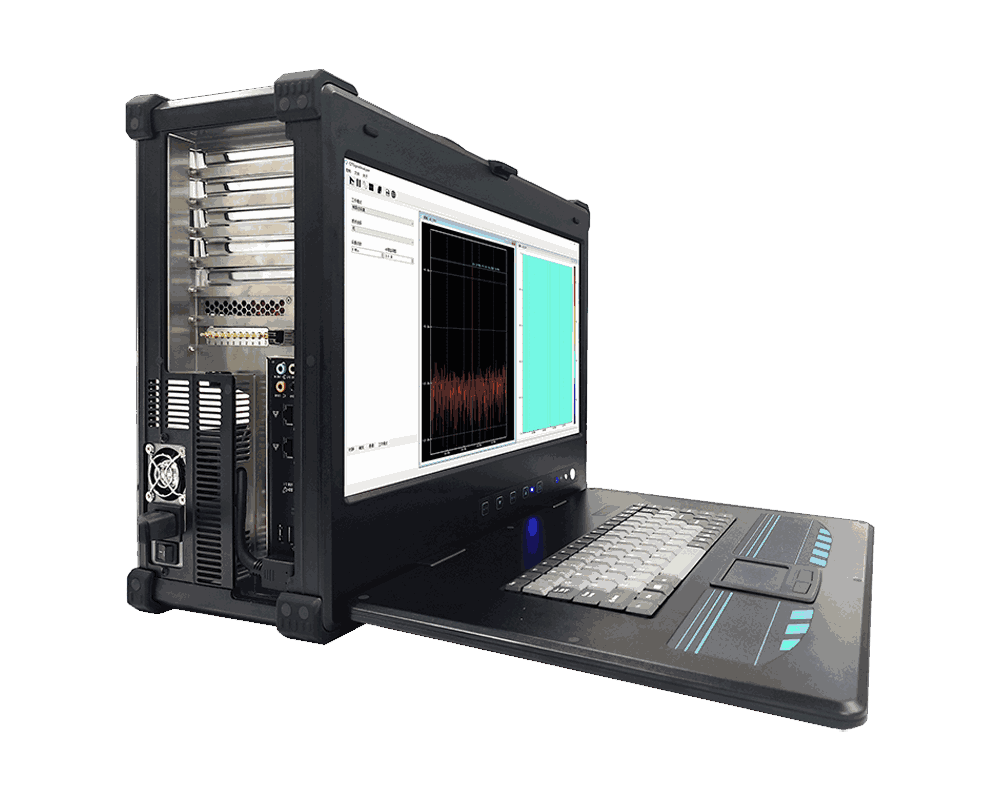

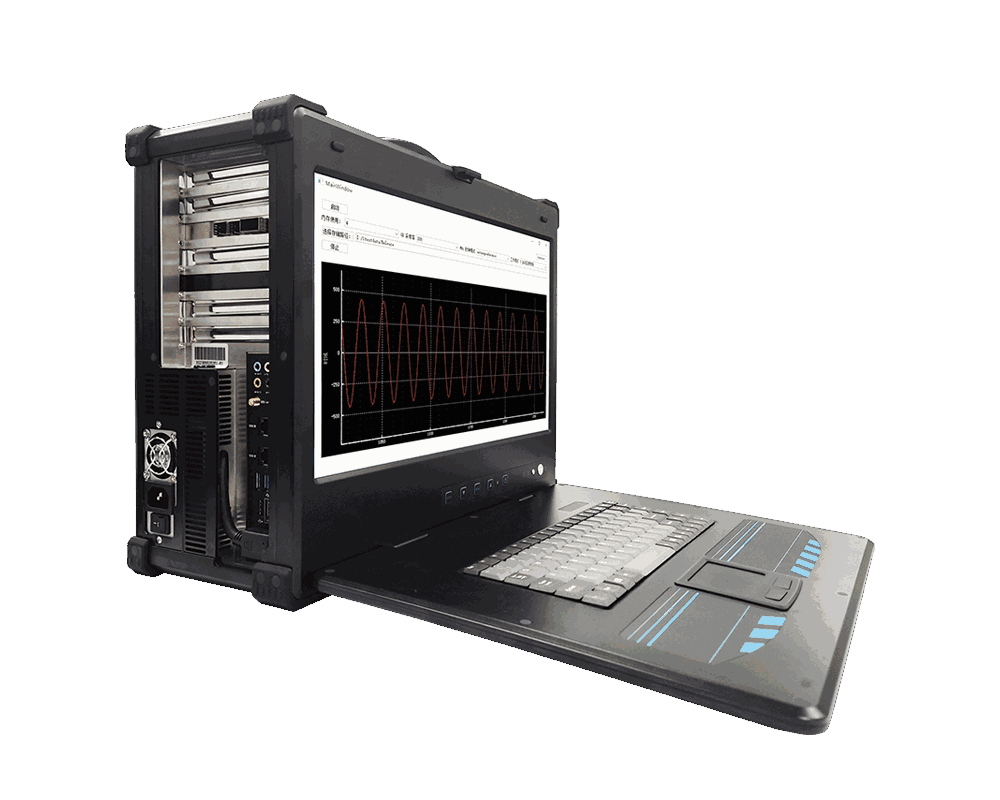

超帶寬MIMO通信測試系統(tǒng)

超帶寬MIMO通信測試系統(tǒng)

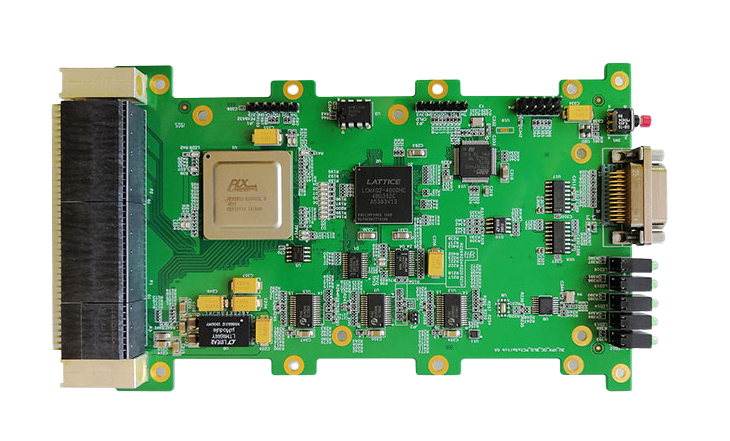

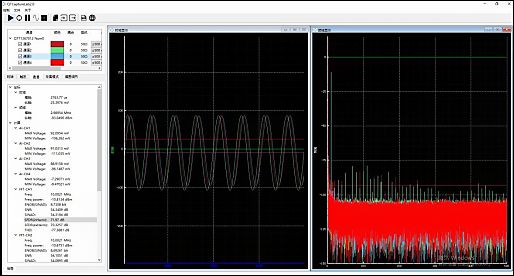

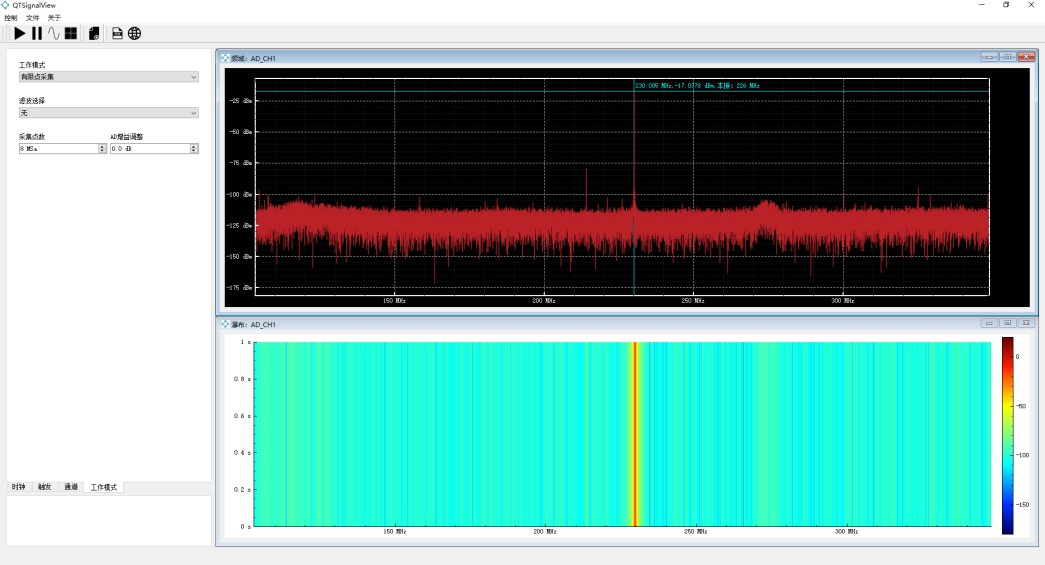

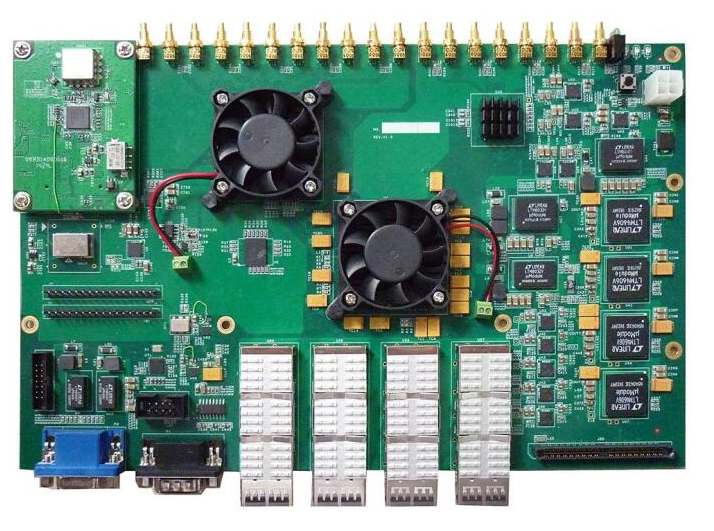

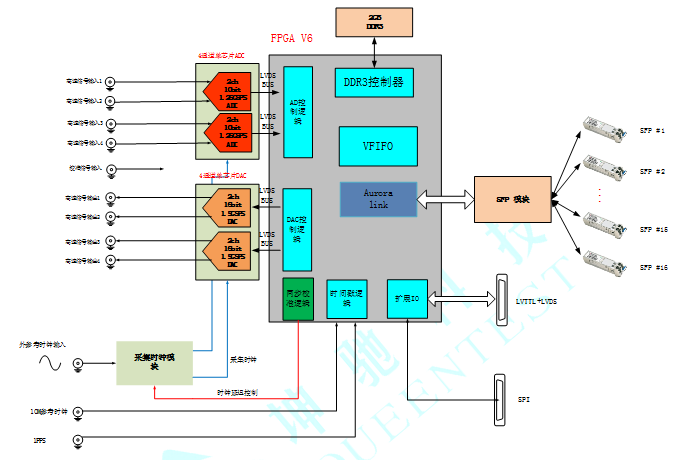

基于光纖接口的超帶寬MIMO通信測試系統(tǒng)可以完成4路寬帶信號收發(fā)(兩對IQ信號)測試,,并進行基于FPGA的實時數(shù)據(jù)處理的目的,。其中AD通道采樣率為10bit,1.25GS/s, DA通道為14bit, 1.5GS/s,。

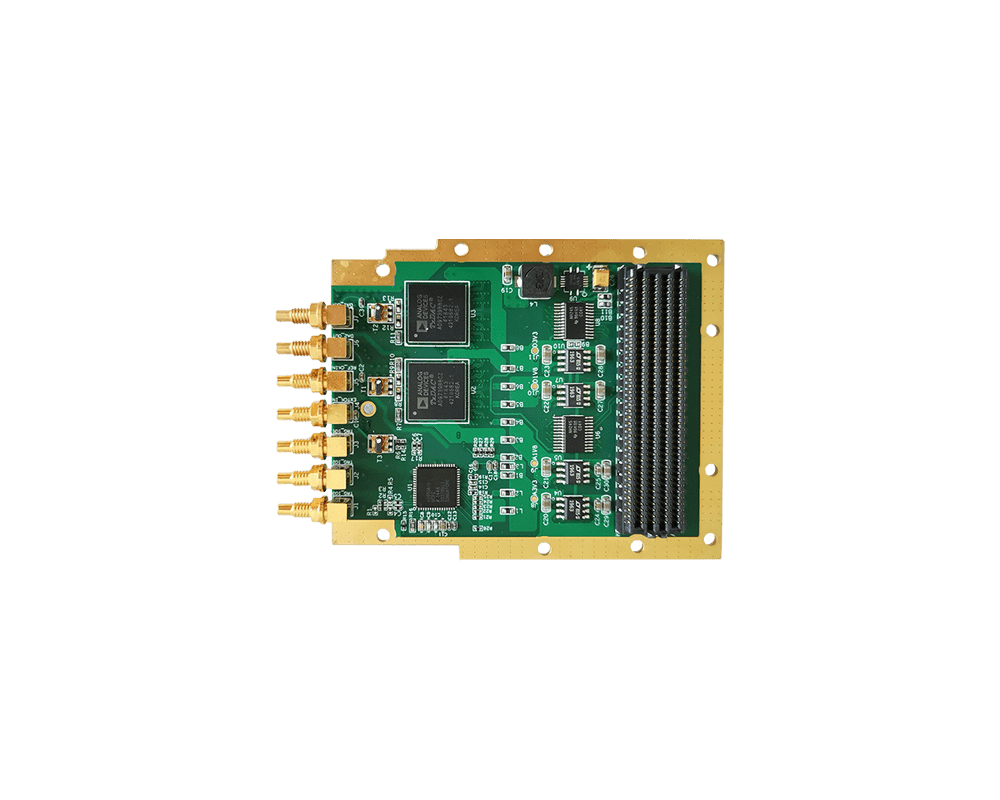

采集模板規(guī)格:

每個模塊集成4通道10bit 1.25GSPS ADC采集,。

同時支持兩對IQ信號輸入,,采用交流差分藕合輸入方式,。

同步模板規(guī)格:

同步采集校準系統(tǒng),。

統(tǒng)一的基準時鐘和觸發(fā)信號分發(fā)。

采集模板實現(xiàn)框圖如下:

ADC規(guī)格如下:

ADC型號:EV10AQ190A

ADC輸出位數(shù):10bit,,4通道采樣率1.25GSPS

模擬帶寬:LF~2GHz

輸入阻抗:100歐(差分),,AC藕合

輸入形式:SMA,差分輸入

滿量程輸入幅度:500mVpp

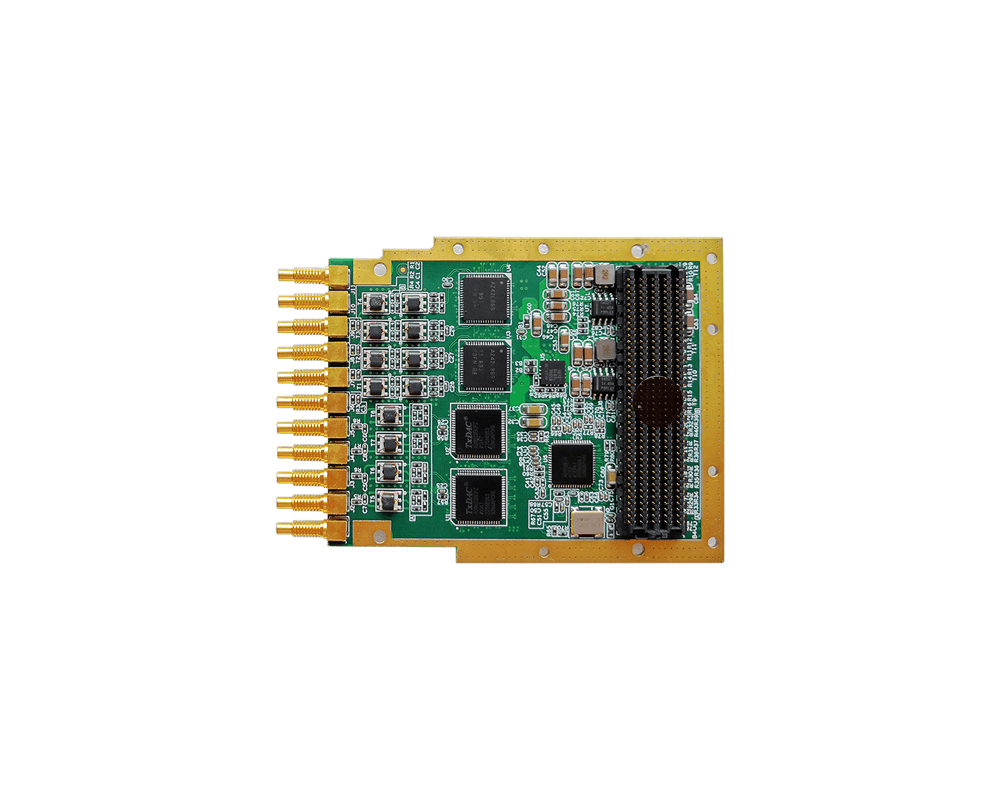

DAC規(guī)格如下:

DAC型號:DAC34SH84

DAC輸出位數(shù):16bit,,4通道采樣率1.5GSPS

輸出阻抗:100歐(差分端),AC藕合

輸入形式:SMA,,差分輸出

滿量程輸出幅度:500mVpp(單端),,1Vpp(差分)

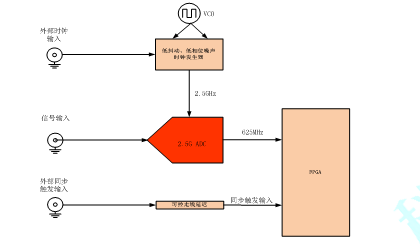

具有同步觸發(fā)和外參考時鐘輸入的采集時鐘模塊:

該模塊為單獨一個PCB子板,可以方便更換,。當更換為不同VCO型號時,,可以支持靈活的輸出采樣時鐘,覆蓋2.5GHz~到1080MHz(時鐘時采樣率的2倍),。

擴展IO:

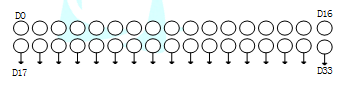

1.DIO

17個

兼容2.5V LVTTL和LVCMOS

連接器:單排2.54mm通用連接器,。

排列如下:

2.高速LVDS輸入輸出

數(shù)量25對

LVDS速度1.25Gbps

連接器:高密度連接器帶連接電纜

3.SPI接口

定義為4線SPI,S_CLK,、S_DIN,、S_DOUT、S_EN,。

3.3V TTL電平,。

連接器:8pin 2.54mm連接器。

4.狀態(tài)LED

4個LED直接連接到FPGA上用于顯示,。

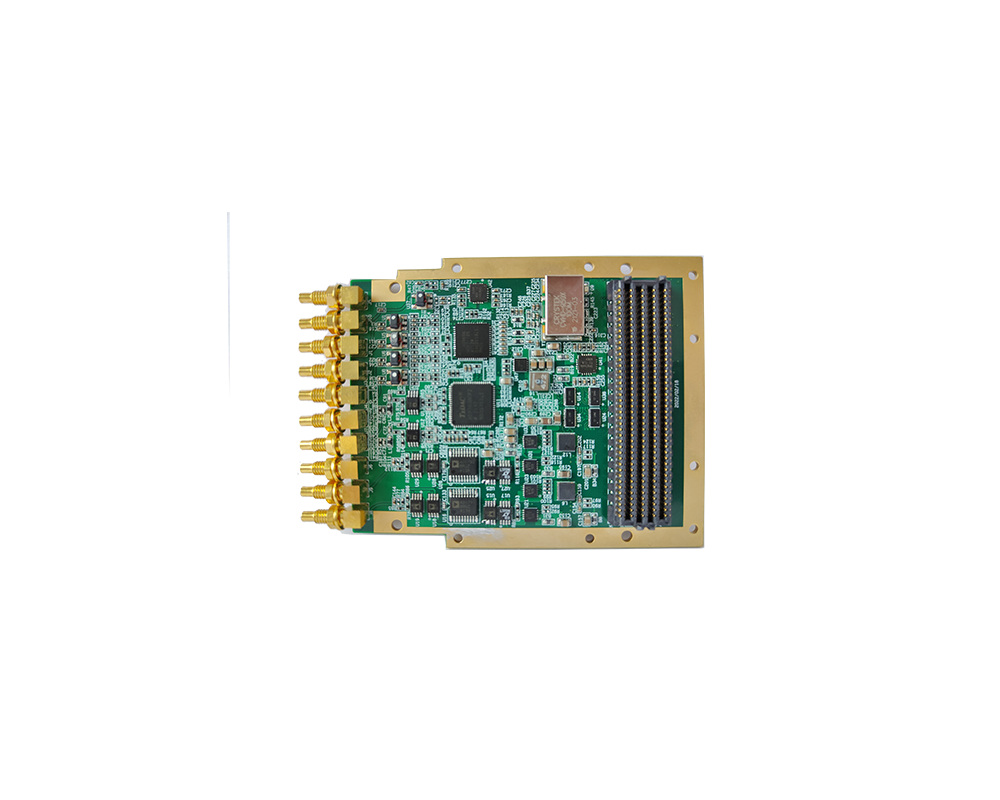

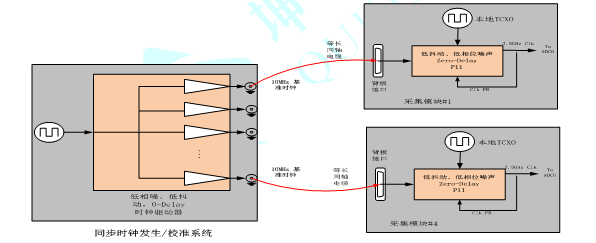

同步模塊:

產(chǎn)生同步四個采集模塊的基準時鐘和同步信號

同步校準信號發(fā)生

通過自動調(diào)節(jié)芯片內(nèi)部的延遲來達到輸出時鐘和參考時鐘的相位一致性,。

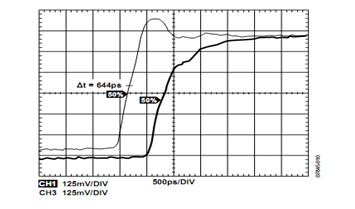

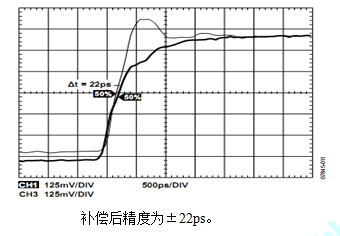

沒有進行zero delay補償?shù)臅r鐘輸入/輸出相位誤差約為664ps,這個誤差是一個范圍,,可能在0-644ps中隨機出現(xiàn),!經(jīng)過zero delay補償?shù)南辔徽`差如下圖:

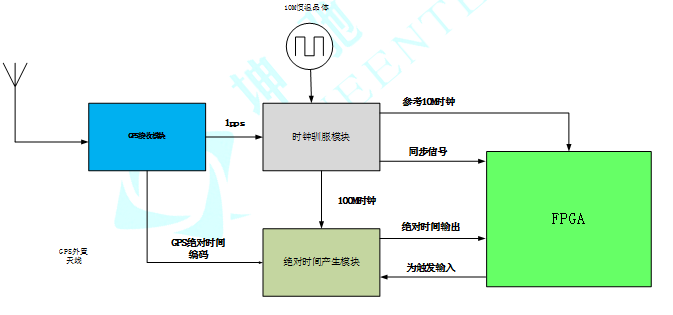

關于秒脈沖同步控制:

GPS同步模塊由以下部分組成:

GPS接收模塊:輸出1pps秒脈沖

本機恒溫晶體:輸出10MHz

時鐘馴服模塊:根據(jù)GPS輸出的1pps信號,同步每個采集模塊的本地恒溫晶體,;同時產(chǎn)生1s頻率的

同步時鐘信號,。

保障在GPS衛(wèi)星短時間失鎖情況下仍然能維持同步穩(wěn)定

采集間模塊同步機制:

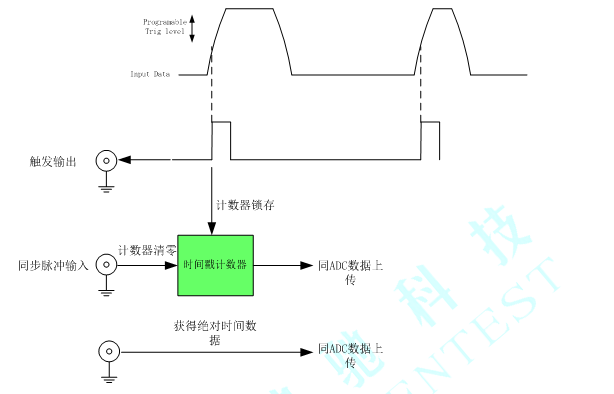

同步原理如下圖所示:

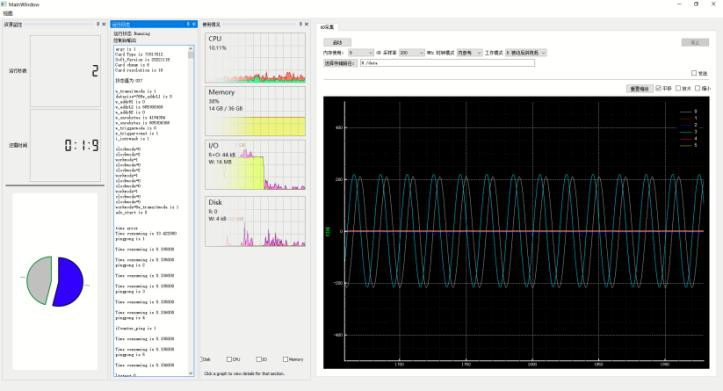

同步機制在采集模塊FPGA內(nèi)實現(xiàn),,采用兩種方式實現(xiàn)同步:

時間戳模式:驅(qū)動時鐘為采集時鐘,頻率1.25GHz,,FPGA2/4分頻處理,,當有觸發(fā)事件時,鎖存時間戳計數(shù)器,,將該計數(shù)器值同ADC數(shù)據(jù)值上傳服務器,。GPS同步模塊輸出的同步脈沖負責每秒為計數(shù)器清除一次,保證各個采集模塊的計數(shù)器同步,。如果各個采集模塊是同時滿足觸發(fā)條件的,,此時各個通道的計數(shù)器值應該相等。

絕對時間記錄模式:觸發(fā)脈沖輸出到GPS絕對時間計數(shù)器中,;當絕對時間計數(shù)器檢測到上升沿,,鎖定絕對時間計數(shù)器,然后通過總線形式讀取當前時間,,同ADC采集數(shù)據(jù)上傳主機,。

-

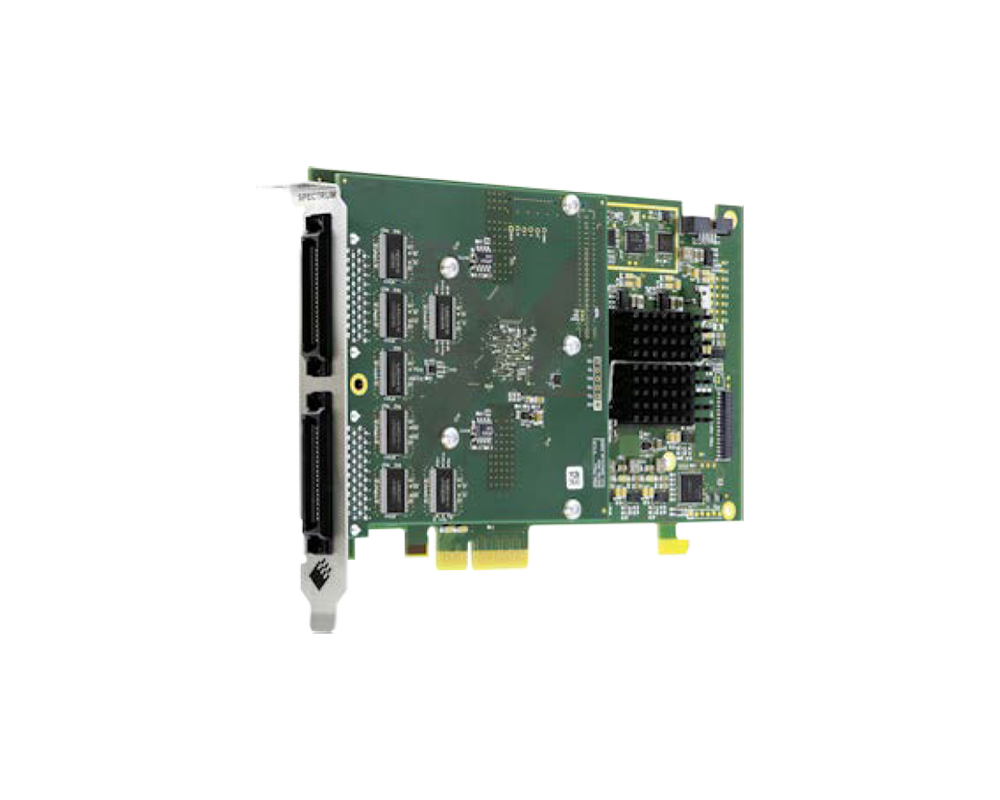

M2p.65xx-16bit任意波形發(fā)生器

8通道任意波形發(fā)生,40-125M信號發(fā)生速率,,16bit轉(zhuǎn)化精度,,±6V信號輸出范圍

-

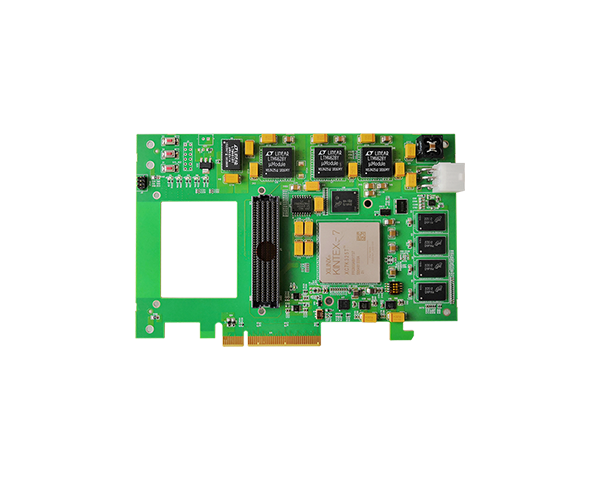

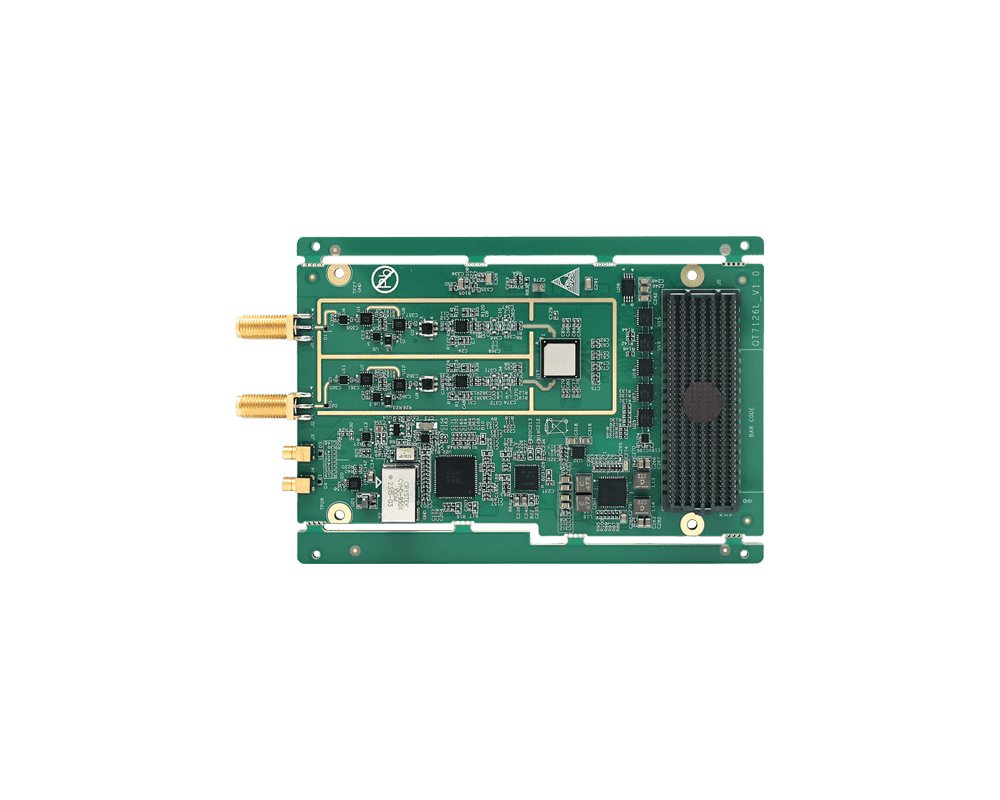

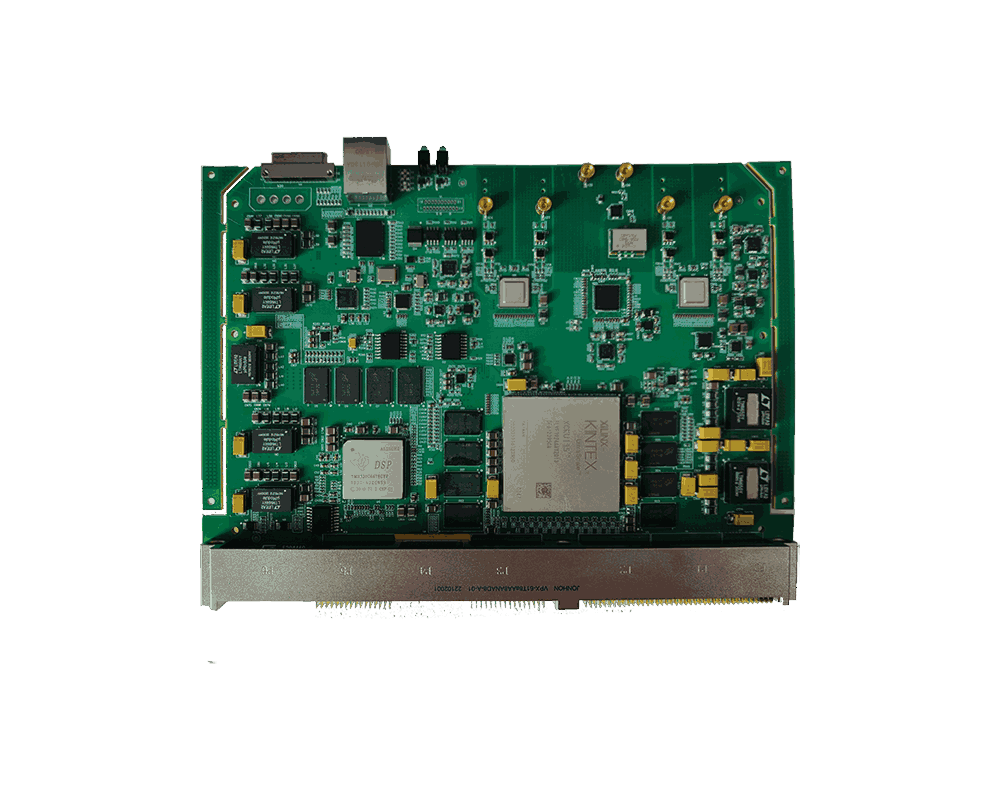

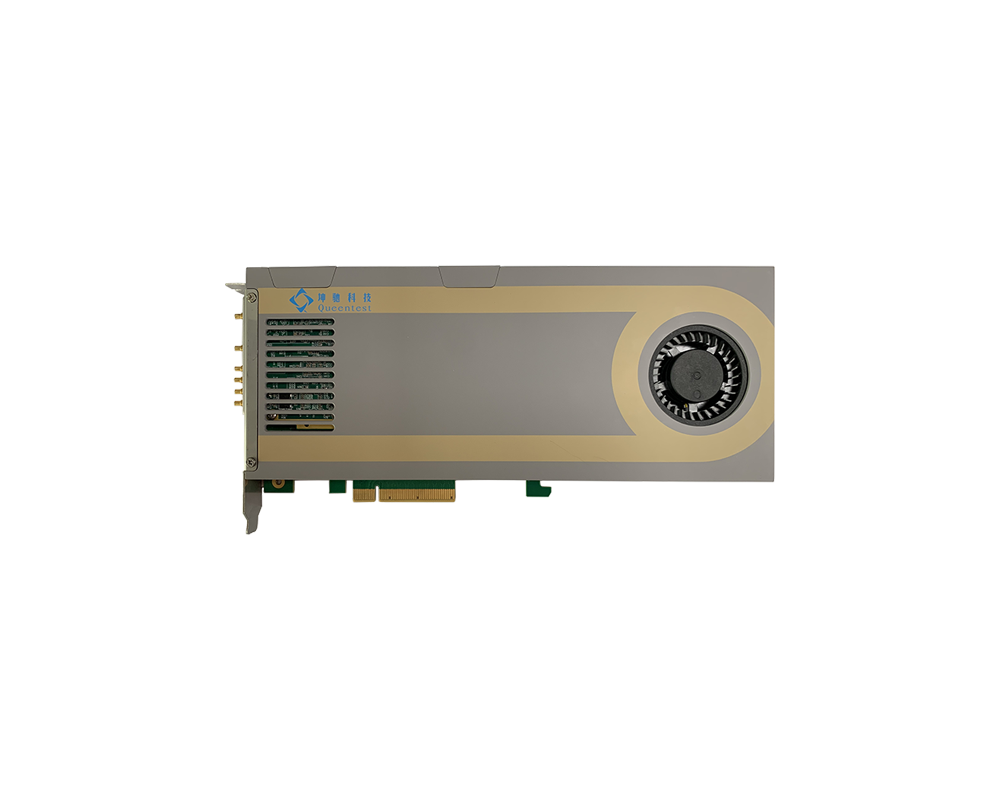

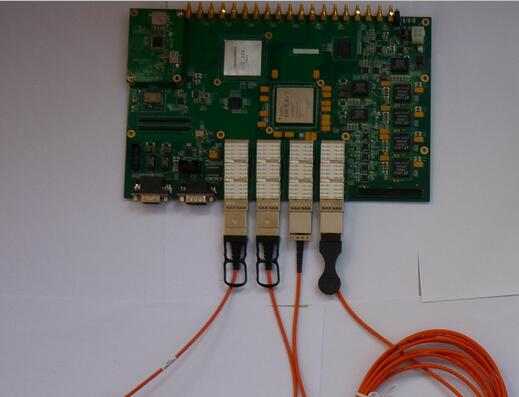

QT7021L-光纖/以太網(wǎng)載板

QT7021L 板卡是一款高性能載板。主控芯片為 1 顆 Xilinx 公司 Virtex-7 系列家族中的XC7V690T-2FFG1761I,,XC7VX690T-2FFG1761I 搭配2 組4 顆16bit/512Mb 的DDR3-1866 SDRAM,, 還搭配了 1 顆 256Mb 的 SPI Flash,

-

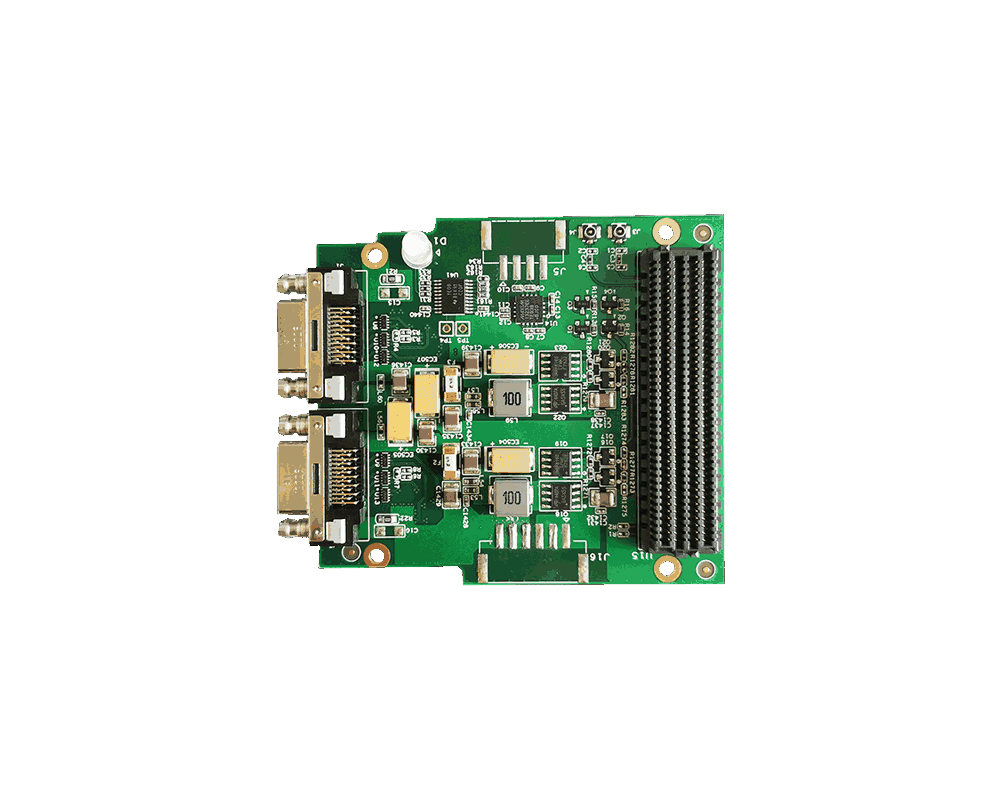

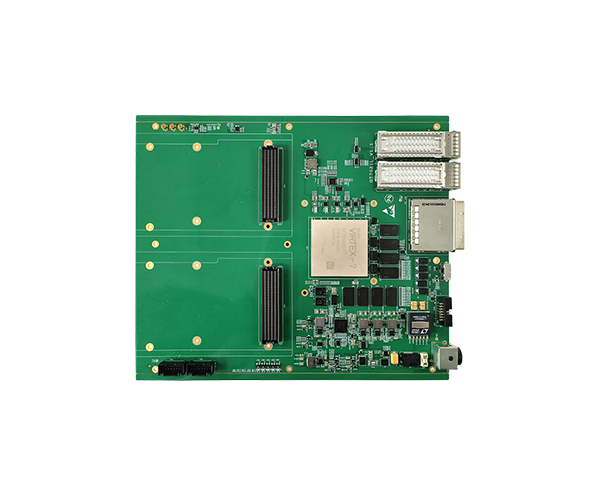

QTC4000H-高速采集記錄儀

高帶寬,、大容量的信號采集記錄

-

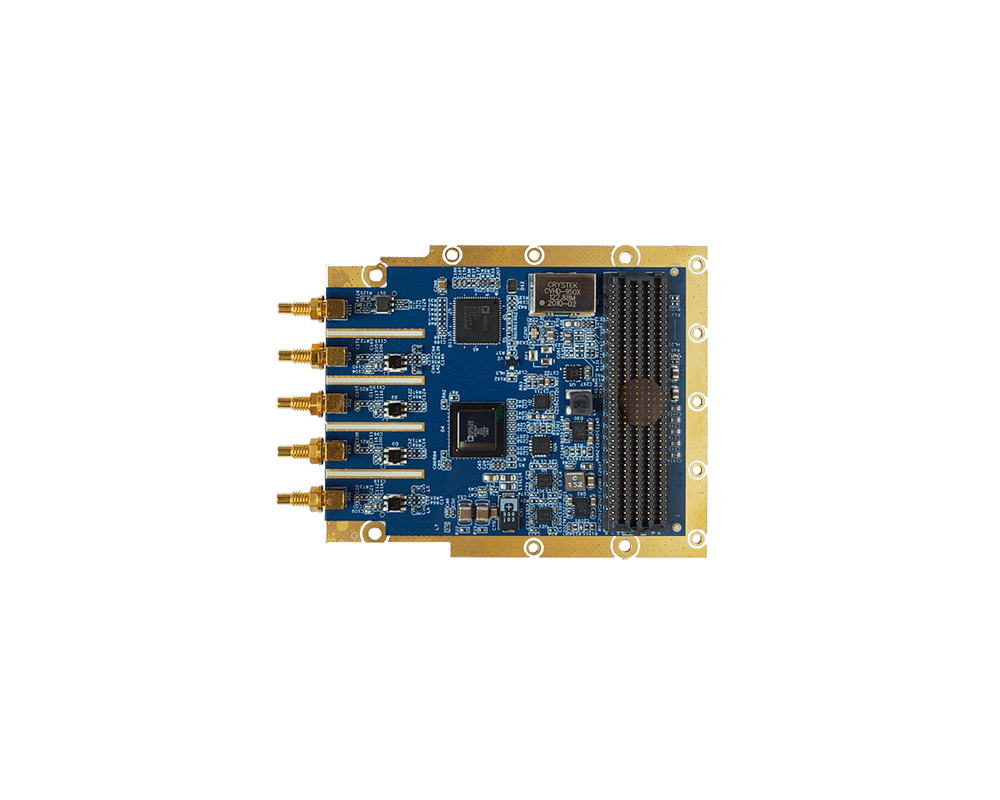

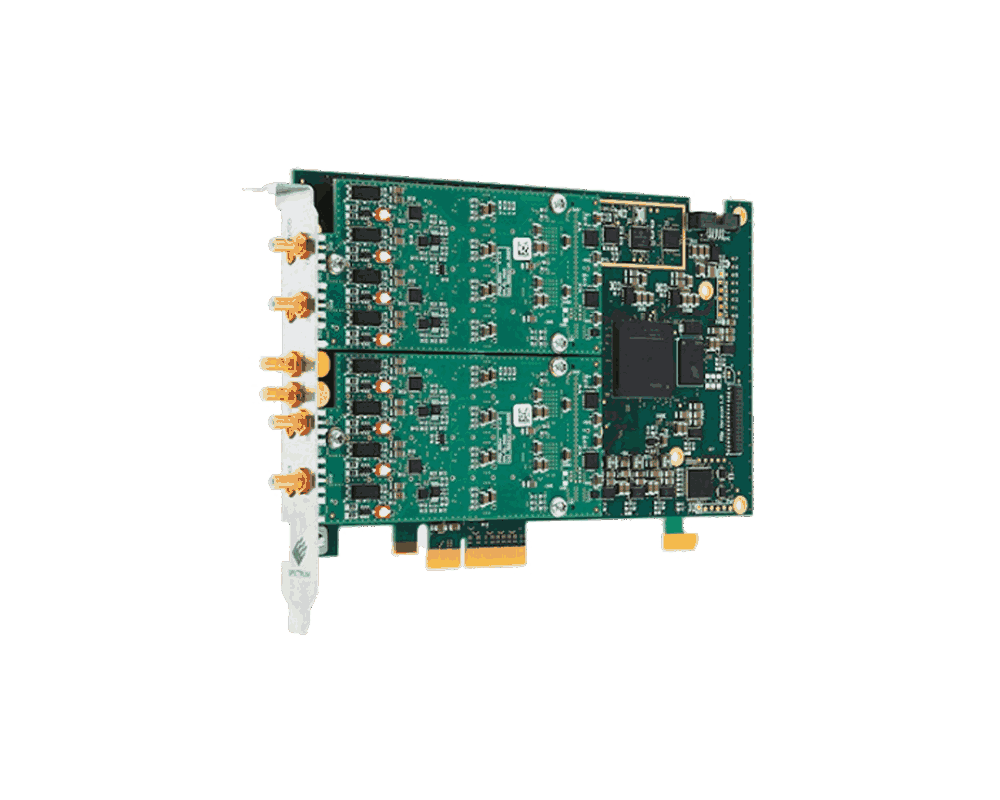

QT20136-寬帶中頻采集卡

交流耦合與雙極性寬帶信號輸入,,4路14位1.0GS/s A/D通道,全功率模擬帶寬(-3 dB)2GHz