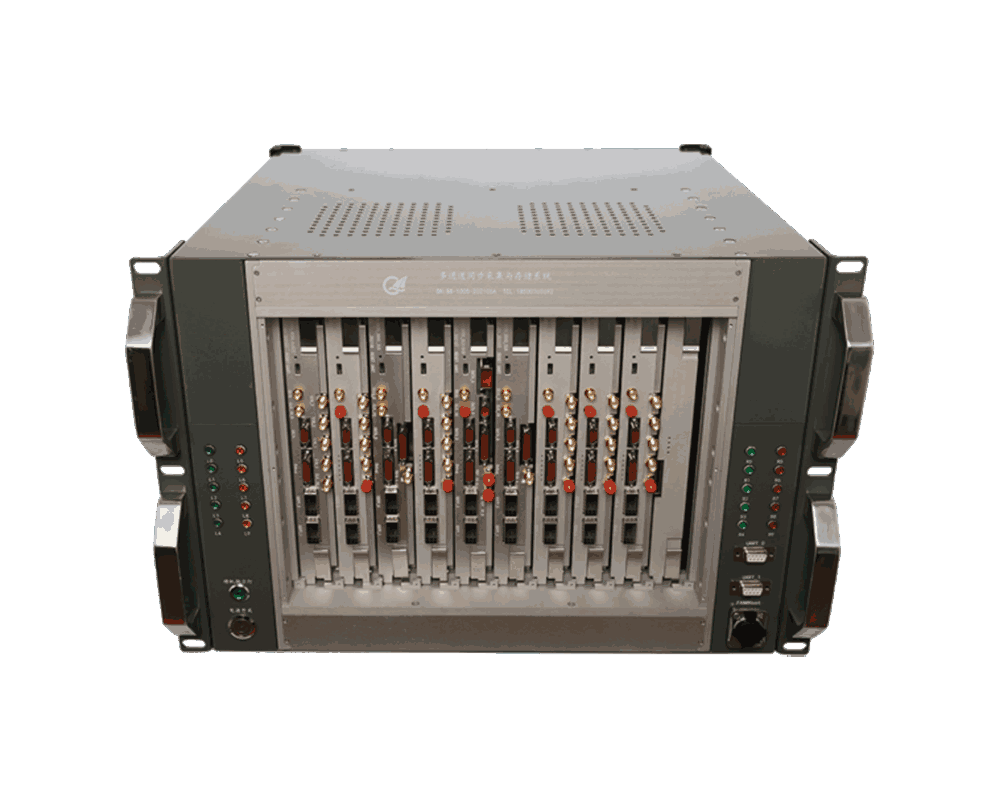

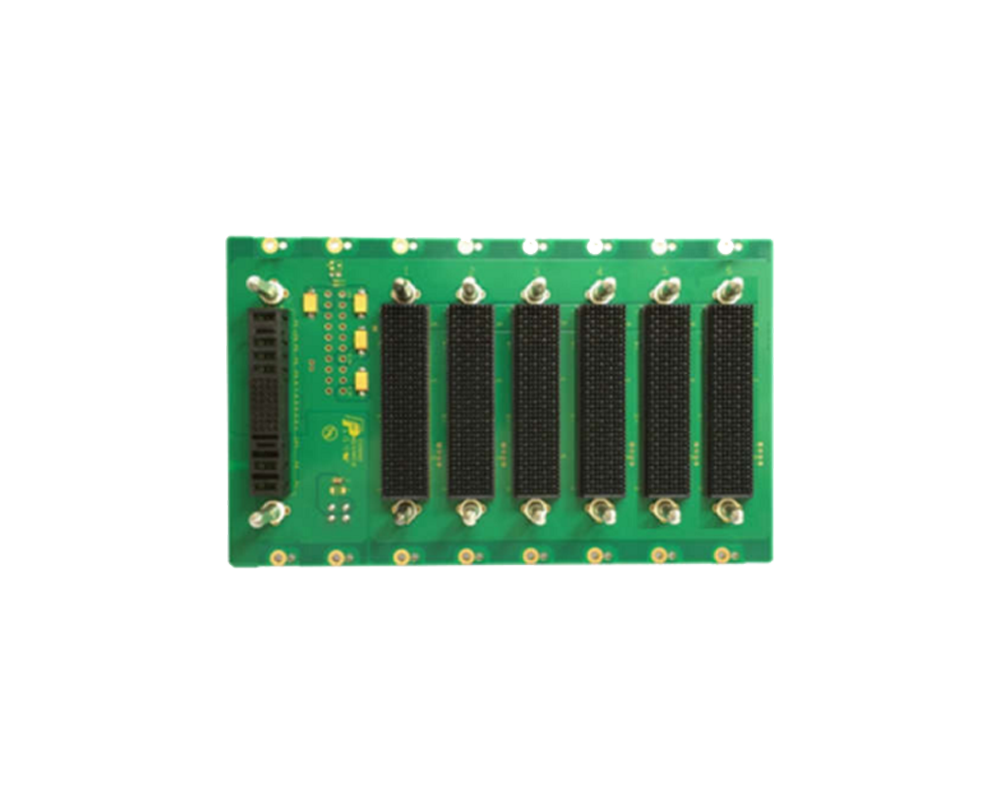

坤馳16通道USB超聲相控陣采集激勵(lì)系統(tǒng)

采集激勵(lì)系統(tǒng)規(guī)格:

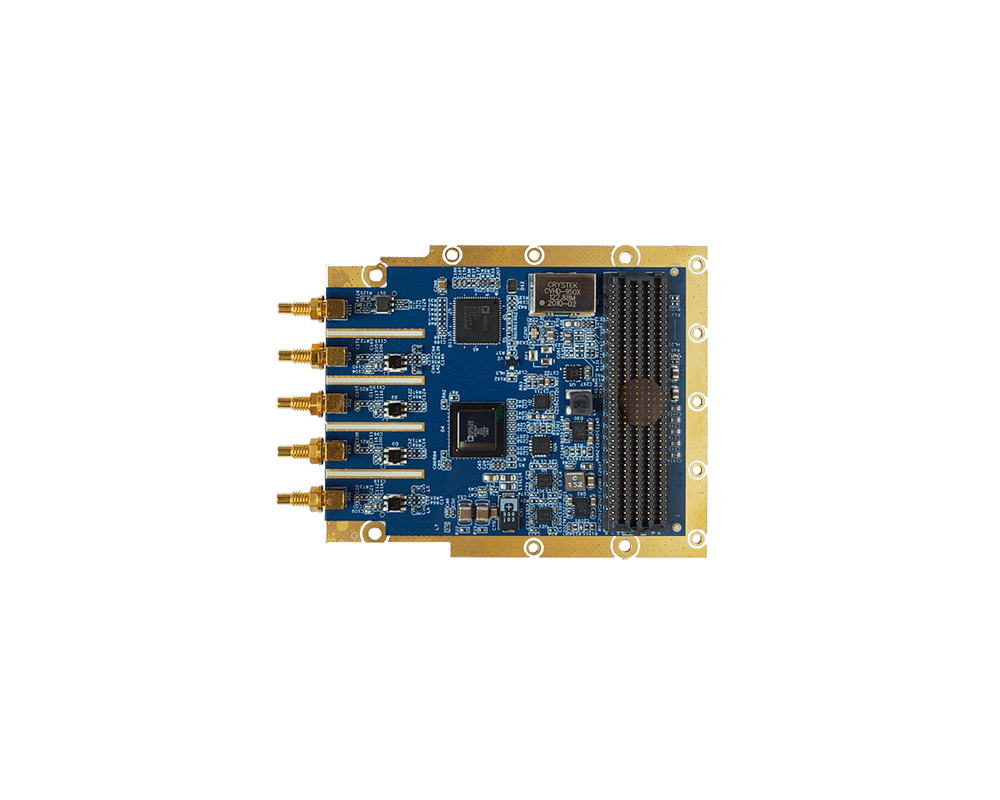

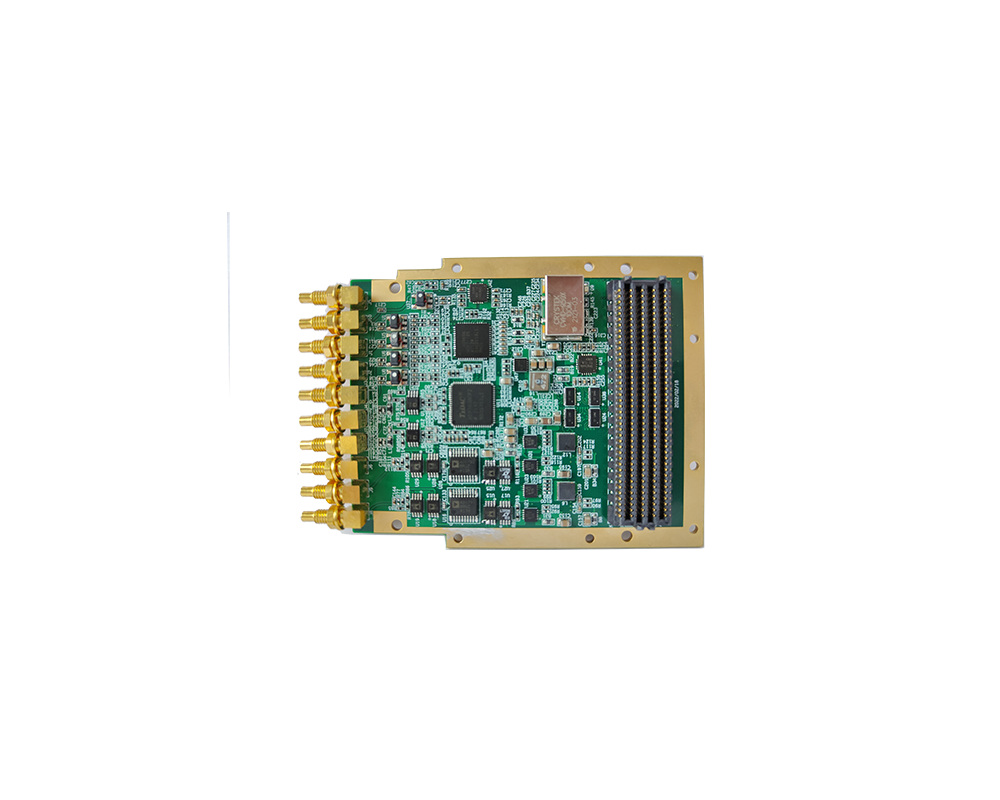

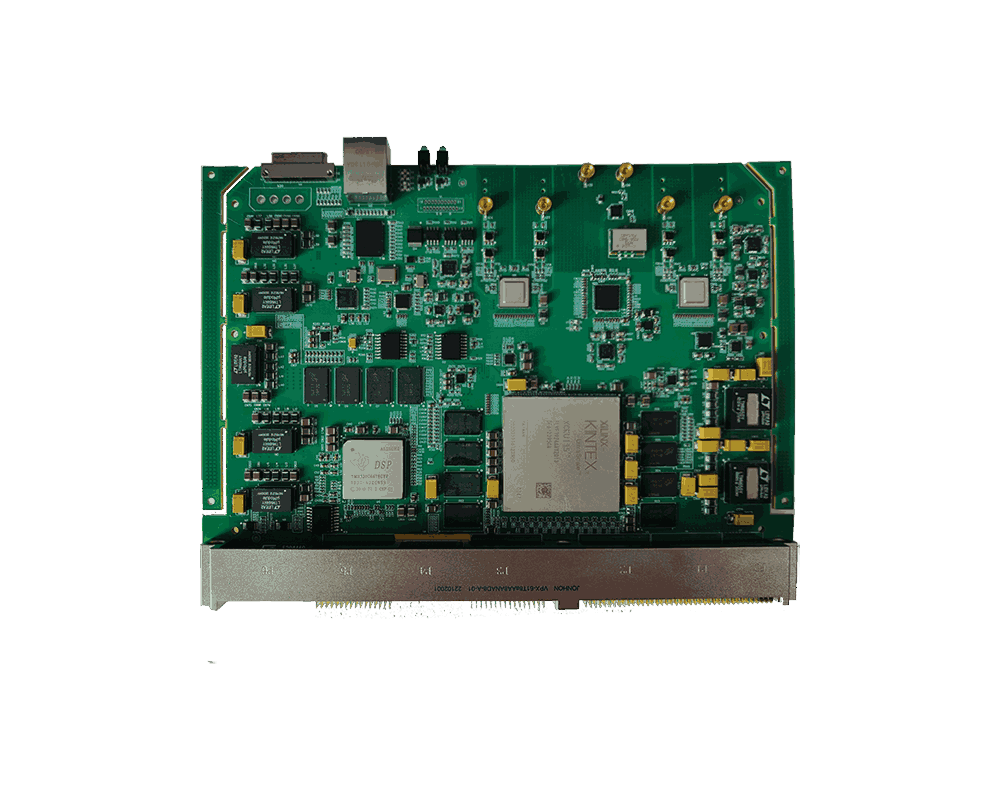

系統(tǒng)采用基于USB2.0的采集系統(tǒng),包括如下幾個(gè)部分:

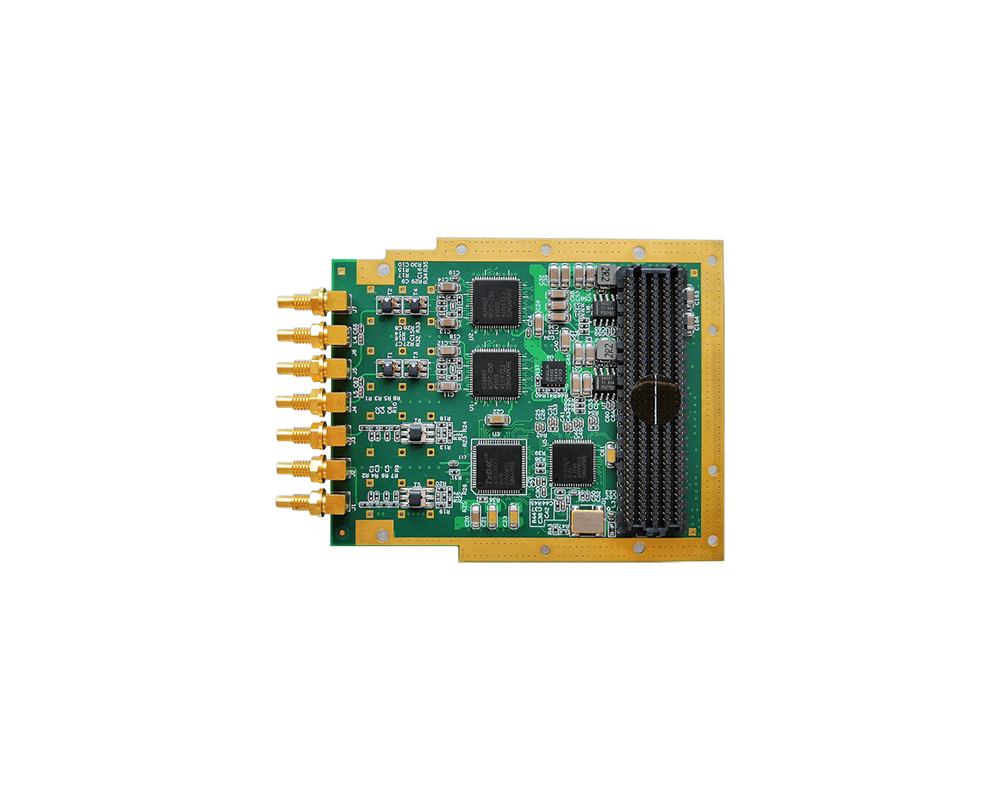

1.12bit40MSPSADC,,16通道,。采樣率可以通過(guò)軟件設(shè)置。

2.12bit40MSPSDAC,,16通道,。時(shí)鐘同ADC同步。

3.低噪聲模擬前端,,支持+/-10V~+/-200mV信號(hào)輸入,,1MΩ/50Ω阻抗可選。

4.輸出幅度5Vpp,,支持50歐姆負(fù)載.

5.板載512MBDDR內(nèi)存,。

6.優(yōu)化的USB2.0傳輸接口,支持33MB/s的連續(xù)傳輸速率,。

7.外時(shí)鐘和外部觸發(fā)輸入,,可以支持多塊板卡級(jí)聯(lián),支持更多通道,。

8.16個(gè)可編程GPIO,,可用于系統(tǒng)控制。

9.高穩(wěn)定度,,超低低抖動(dòng)時(shí)鐘發(fā)生器,。

10.低噪聲電源設(shè)計(jì),。

11.板載高精度自適應(yīng)校準(zhǔn)電路及算法。

12.采用xilinxXC5VSX95T大規(guī)模FPGA,,提供用戶(hù)FPGA邏輯開(kāi)發(fā)支持,,可用于相控陣超聲算法開(kāi)發(fā),其中內(nèi)部時(shí)鐘可以工作在500MHz,。

13.寬溫設(shè)計(jì)0℃~+70℃

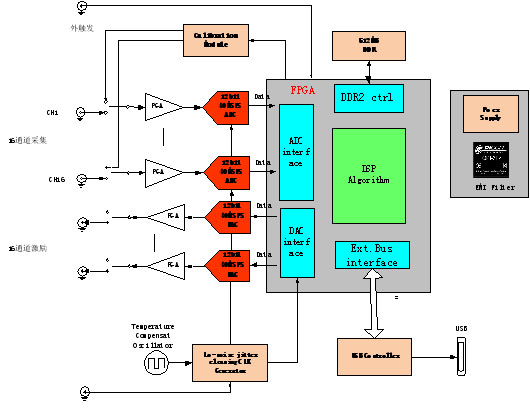

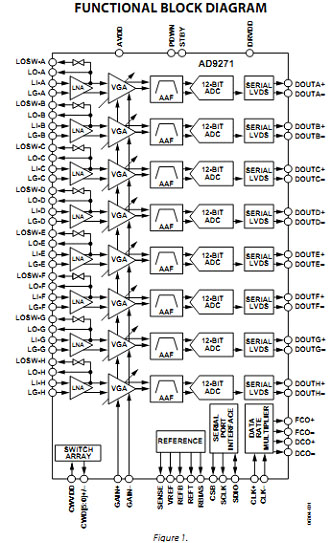

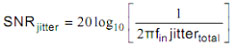

系統(tǒng)整體框圖如下:

方案描述:

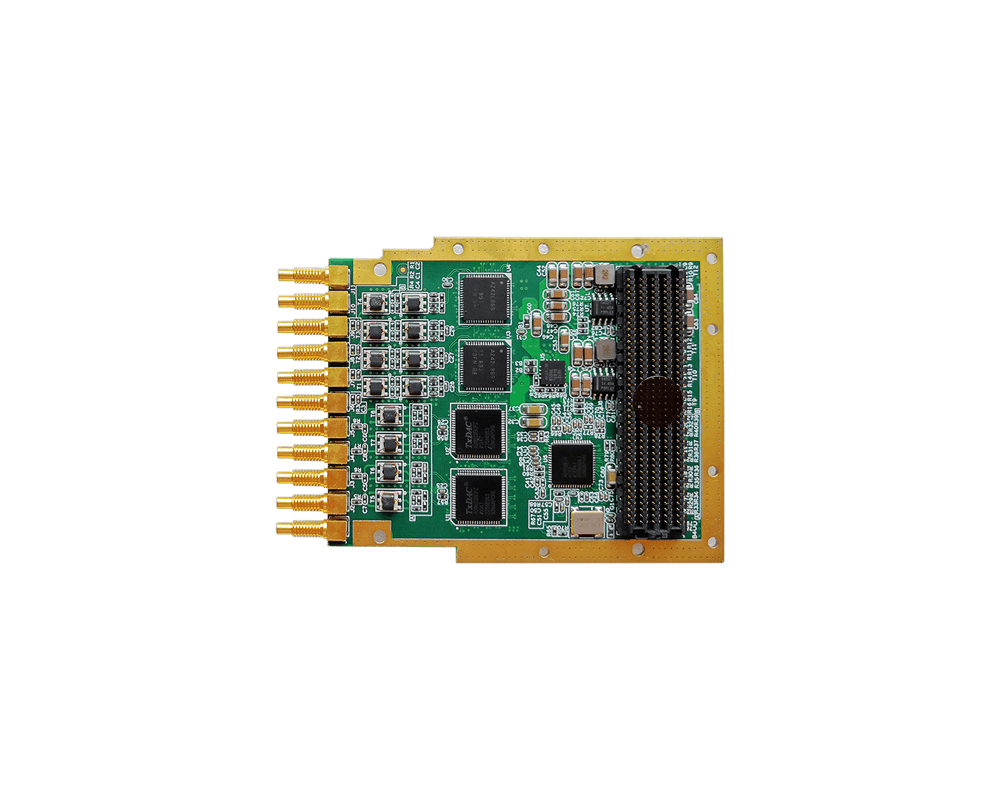

該采集系統(tǒng)主要用于采集16通道和同時(shí)放送16通道發(fā)送信號(hào),,其設(shè)計(jì)任務(wù)有以下幾點(diǎn):

1.采集發(fā)射同步進(jìn)行,同步采集返回的脈沖信號(hào),。

2.16通道精確同步采集和精確同步信號(hào)發(fā)送,。

3.將采集完成的數(shù)據(jù)以及計(jì)算結(jié)果通過(guò)USB接口傳出上位機(jī)。

4.保證ADC和DAC的SNR以及長(zhǎng)時(shí)間寬溫的工作穩(wěn)定性,。

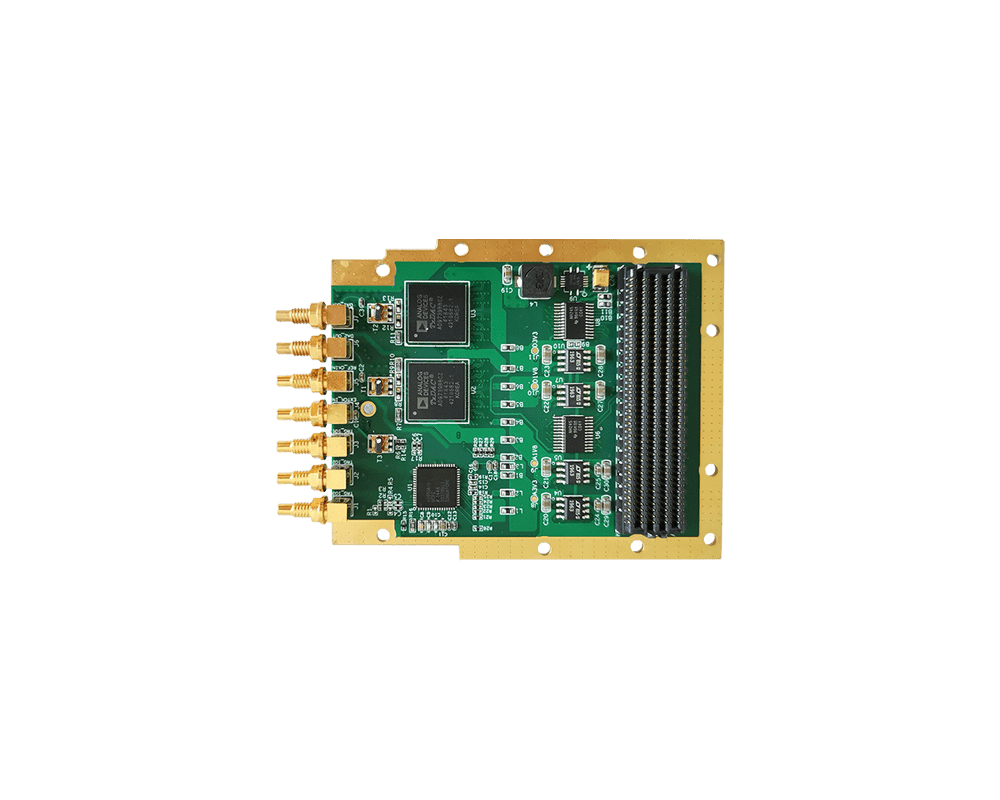

ADC選用ADI公司專(zhuān)為超聲陣列采集開(kāi)發(fā)的專(zhuān)用采集芯片AD9271,。該芯片集成8通道12bit40MHzADC,每通道更是集成信號(hào)調(diào)理和抗混疊濾波器,,大大減少板上芯片面積,。

該芯片系統(tǒng)框圖如下:

多通道同步采集設(shè)計(jì)難點(diǎn)和解決辦法:

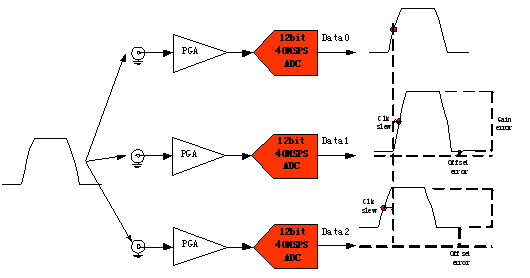

1.首先要保證多通道的時(shí)鐘嚴(yán)格同步以及每通道的模擬電路以及每個(gè)ADC的工作狀態(tài)一致性。如下圖所示:

各個(gè)通道的采集誤差主要由模擬電路以及不同ADC芯片的clkslew,,gainerror以及offseterror組成,,這些誤差的引入,都會(huì)引起峰值電路的誤判(半峰/全峰值檢測(cè)均是如此),。盡管我們?cè)谠O(shè)計(jì)硬件電路以及PCB設(shè)計(jì)會(huì)盡量考慮以上問(wèn)題,,如同源的時(shí)鐘分布以及相同的走線(xiàn),;多個(gè)ADC公用精準(zhǔn)的外部參考電壓源等等,,但不幸的是,這些設(shè)計(jì)改進(jìn)并不能完全消除這些由模擬器件本身的固有特性引起的誤差,,這些誤差是隨機(jī)的,,也隨溫度變化而變化的。

因此,,動(dòng)態(tài)校正電路以及自適應(yīng)的數(shù)字后補(bǔ)償算法是必不可少的解決方案,。

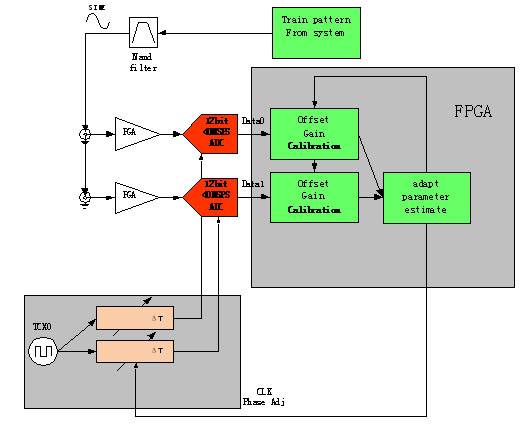

校正功能實(shí)現(xiàn)原理如下:

校正功能有校正電路和FPGA算法部分組成,校正電路由高精度低速DAC,,參考源,,濾波器和時(shí)鐘相位微調(diào)芯片組成。FPGA算法核心為參數(shù)估計(jì)自適應(yīng)算法和校正參數(shù)邏輯組成,。校正目標(biāo)為設(shè)置一個(gè)基準(zhǔn)通道,,第2個(gè)通道的時(shí)鐘相位以及gain和offset向該基準(zhǔn)通道標(biāo)定。該方法不能校準(zhǔn)每通道ADC的絕對(duì)精度,,而只是每通道的個(gè)參數(shù)一致,,這對(duì)測(cè)量每通道采集數(shù)據(jù)的相對(duì)相位是足夠了,!

校準(zhǔn)信號(hào)為A*sin(ω*t+φ)+B;

CH0采到的信號(hào)為A0*sin(ω*t+φ0)+B0;

CH1采到的信號(hào)為A1*sin(ω*t+φ1)+B1;

通過(guò)迭代法解線(xiàn)性方程組,當(dāng)方程收斂時(shí),,分別能得到每個(gè)通道的參數(shù),,通過(guò)計(jì)算每個(gè)通道的同基準(zhǔn)誤差,來(lái)調(diào)節(jié)clkphase以及gain和offset來(lái)后是3個(gè)通道工作一致,。

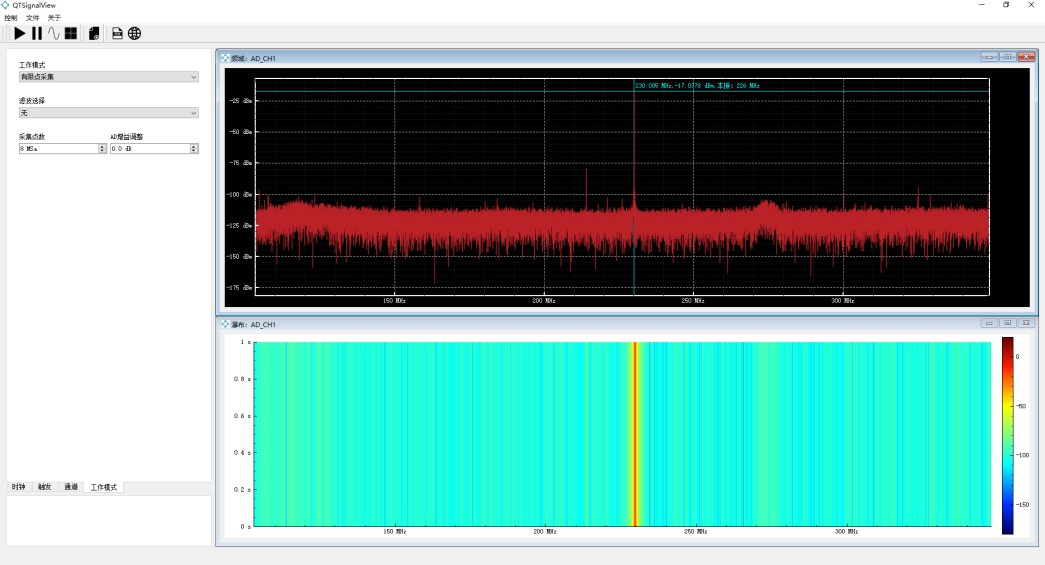

2.為了準(zhǔn)確的采集,,采集系統(tǒng)的信噪比SNR必須得到保證。影響采集精度的主要要素有以下幾點(diǎn):

l量化誤差,。

lClockjitter和ADCjitter,。

l數(shù)字以及電源干擾

量化精度的提高:

對(duì)于量化誤差對(duì)采集系統(tǒng)的影響,我們?cè)谠撓到y(tǒng)中選用14bit的ADC,,理論量化精度

![]() (N=14)

(N=14)

Clockjitter的消除:

該方案中采用溫度補(bǔ)償晶體TCXO以及業(yè)內(nèi)頂級(jí)的JittercleaningCLKGenerator芯片來(lái)保證clock的穩(wěn)定性,,Clockjitter的消除以及極低的Phasenoise。

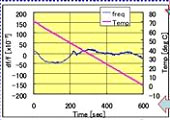

在寬溫工作環(huán)境下,,普通的晶體隨著工作溫度的變化,,晶體的穩(wěn)定度和頻率都會(huì)發(fā)生改變,為解決該問(wèn)題,,我們?cè)谠O(shè)計(jì)中選用epson公司的TCXO,,該晶體具有業(yè)內(nèi)領(lǐng)先的溫度穩(wěn)定性,在寬溫工作環(huán)境下不會(huì)超過(guò)+/-2ppm,,其溫度測(cè)試性能如下:

對(duì)于時(shí)鐘芯片的選擇,,也是基于同樣的考慮,集成高精度高穩(wěn)定的VCO,,具有Jittercleaning功能和clkphaseadj功能,。通常,jitter由ADC本身的jitter和CLKjitter組成,,各自的RMS再組成總jitter的RMS:

![]()

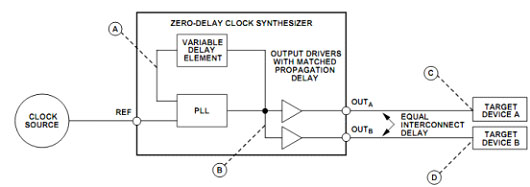

總jitter的RMS會(huì)在采集系統(tǒng)中產(chǎn)生白噪聲,,其關(guān)系如下:

采集系統(tǒng)的總

![]()

采用本時(shí)鐘解決方案,其總的clockjitter在系統(tǒng)中完全能做到<1ps,。在忽略信號(hào)noise,,DNL等情況下,fin和clockjitter有如下關(guān)系:

多通道DAC的一致性考慮:

每個(gè)DAC的參考源均存在差異,,致使每通道的電壓值輸出并不一致,,我們采用以下幾個(gè)方面來(lái)減小電壓的不一致性:

1.采用精密匹配電阻網(wǎng)絡(luò),每個(gè)電阻均采用0.1%精度的低溫漂移電阻,。

2.所有DAC采用外部精密低溫漂參考源

3.采用繼電器切換矩陣自環(huán)回校準(zhǔn),。

具體實(shí)現(xiàn)框圖如下:

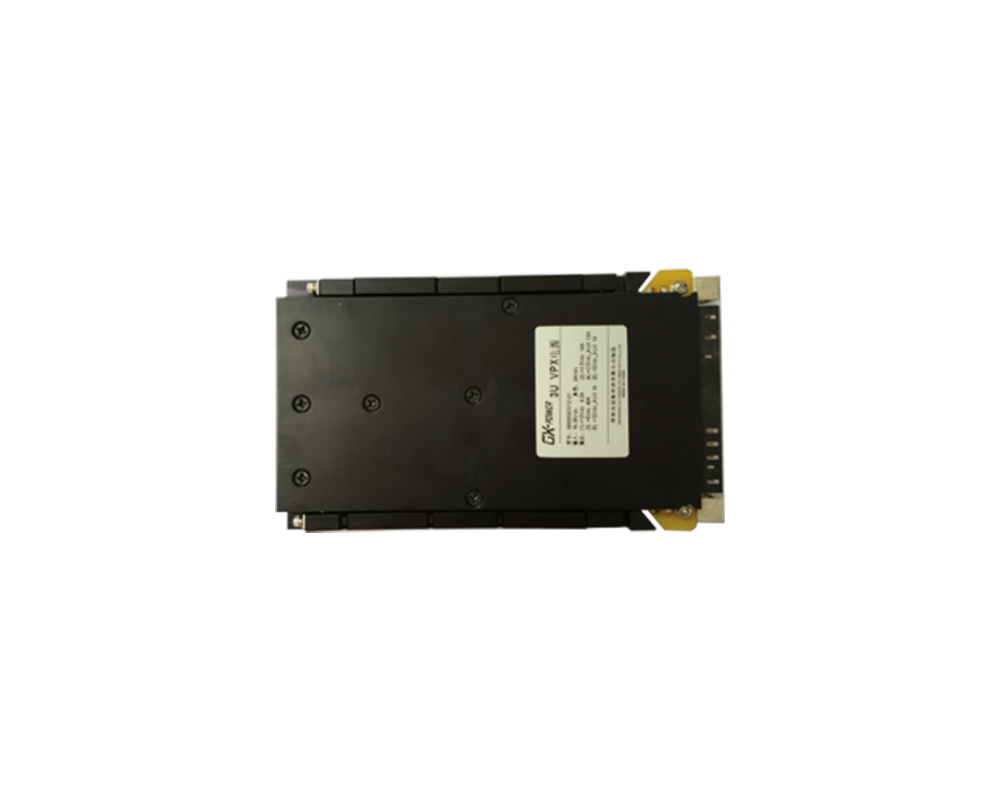

系統(tǒng)電源干擾的解決方案:

1.電源抑制(PSR)是采集系統(tǒng)的比較重要的指標(biāo),高的PSR能擬制電源上的CML共模噪聲,該方案中選用的ADC具有80dB以上的電源擬制比,。

2.有效的數(shù)字-模擬電源隔離和濾波電路,。本方案中采用PICOR的專(zhuān)業(yè)有源EMI濾波器,能在電源上產(chǎn)生65dB的共模制比和80dB的差模擬制比,,遠(yuǎn)遠(yuǎn)高于通用的磁珠等EMI濾波效果,。

3.合理的PCB布線(xiàn)和接地

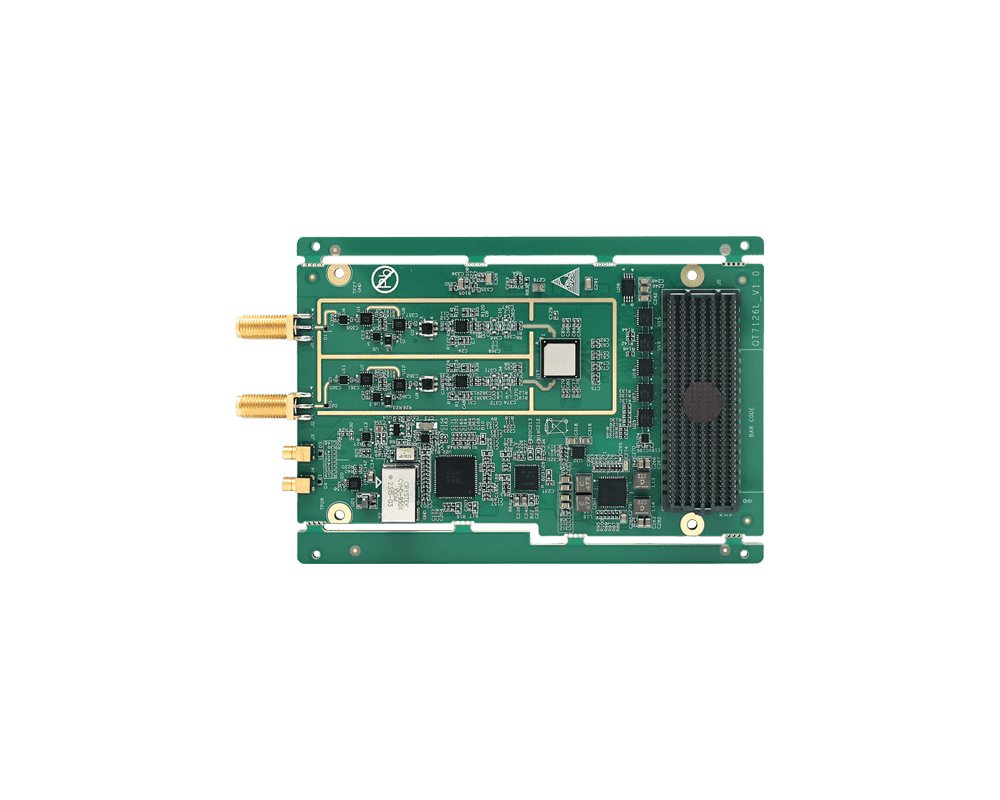

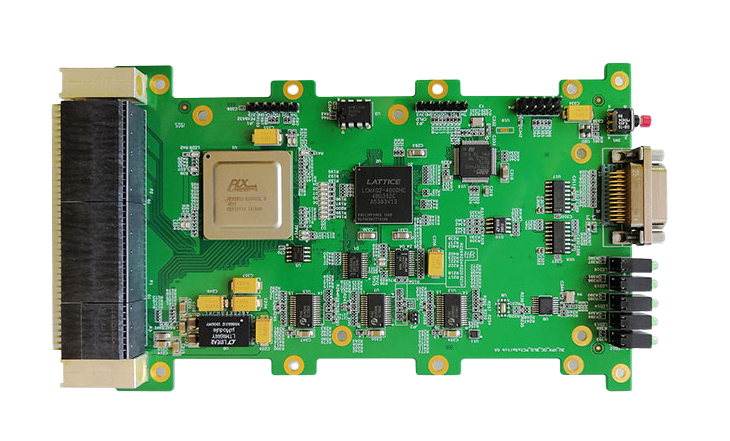

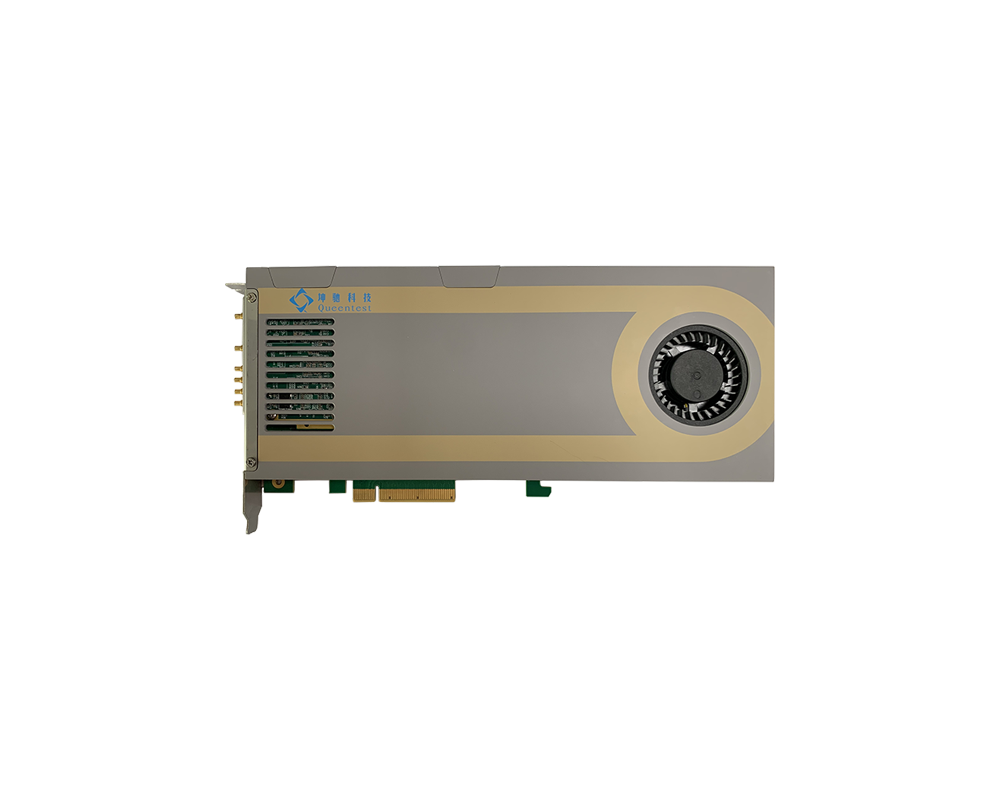

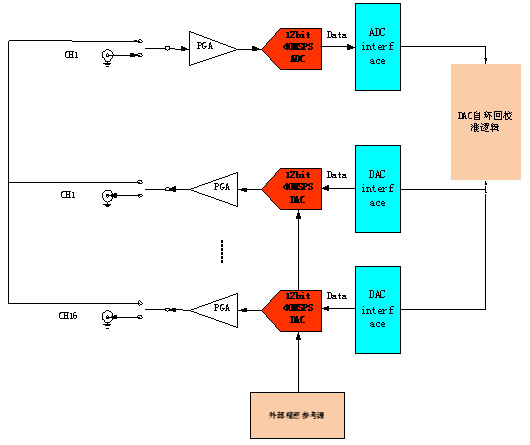

多模塊級(jí)聯(lián)功能擴(kuò)展:

本方案支持多個(gè)模塊級(jí)聯(lián),擴(kuò)展為32通道,,64通道等同步采集激勵(lì)模式,。

具體實(shí)現(xiàn)如下:

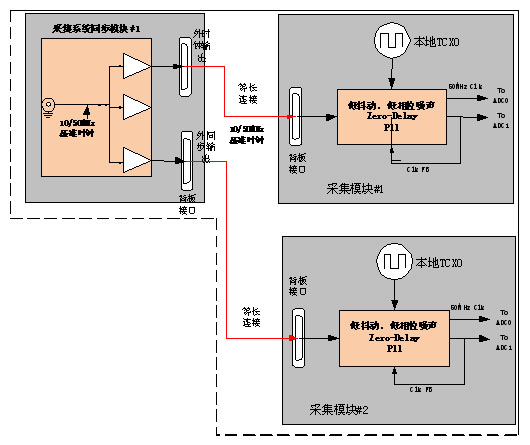

在所有傳輸過(guò)程中,時(shí)鐘和觸發(fā)均使用等長(zhǎng)的傳輸線(xiàn)連接,,基準(zhǔn)時(shí)鐘為10MHz,。采用低頻的基準(zhǔn)時(shí)鐘有助于減少干擾和傳輸中時(shí)鐘的jitter。在采集模塊及ADC輸入信號(hào)端,,我們采用zerodelay時(shí)鐘發(fā)生器進(jìn)行基準(zhǔn)時(shí)鐘和每個(gè)ADC采集時(shí)鐘的相位同步,,其zerodelaypll如下圖所示:

通過(guò)自動(dòng)調(diào)節(jié)芯片內(nèi)部的延遲來(lái)達(dá)到輸出時(shí)鐘和參考時(shí)鐘的相位一致性。

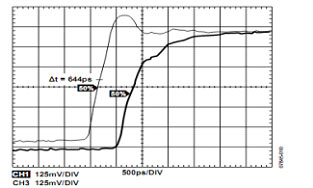

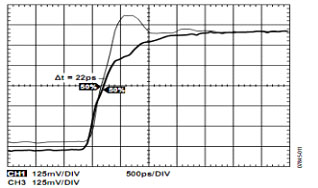

沒(méi)有進(jìn)行zerodelay補(bǔ)償?shù)臅r(shí)鐘輸入/輸出相位誤差約為664ps,,這個(gè)誤差是一個(gè)范圍,,可能在0-644ps中隨機(jī)出現(xiàn)!經(jīng)過(guò)zerodelay補(bǔ)償?shù)南辔徽`差如下圖:

其不確定的相位誤差可以控制在22ps以?xún)?nèi),。

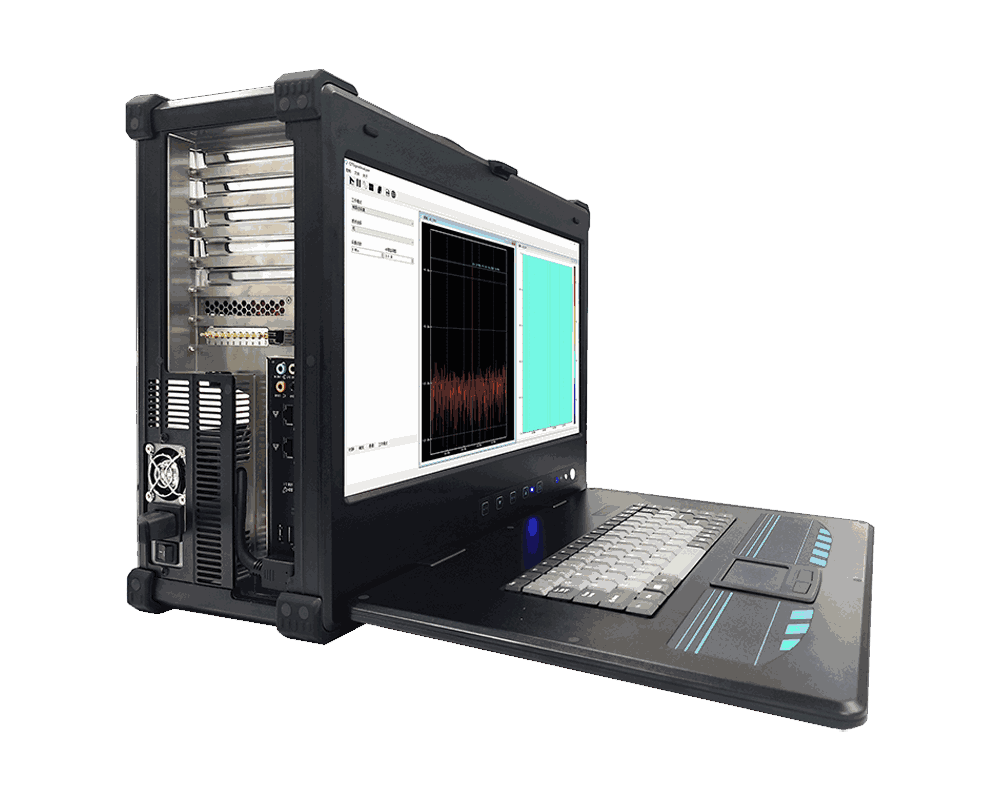

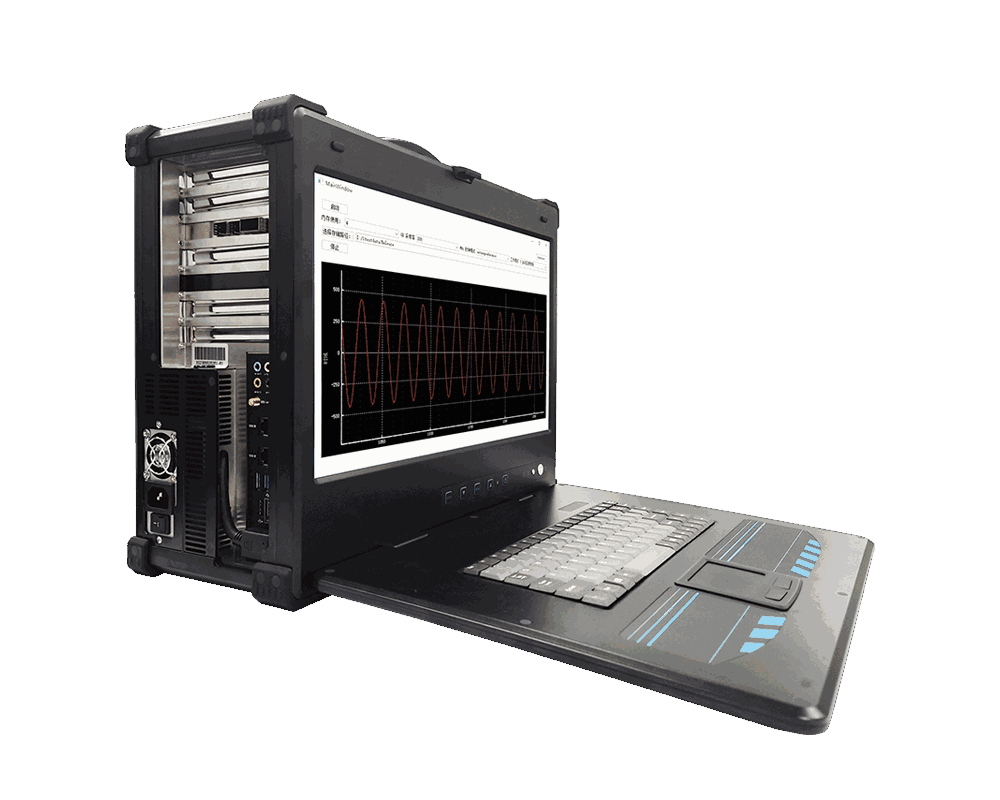

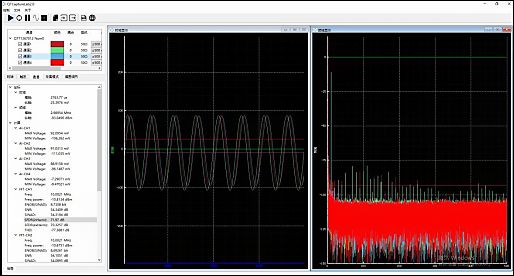

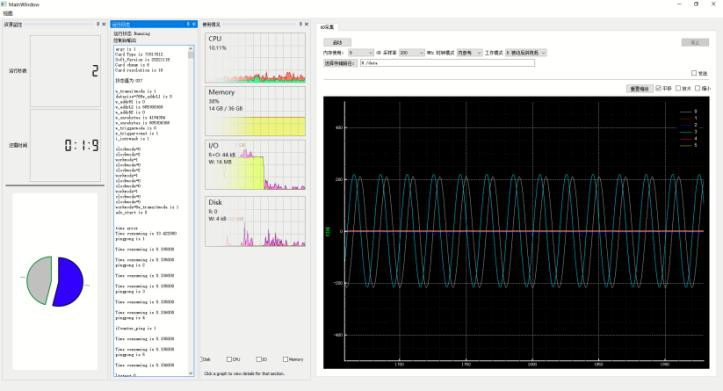

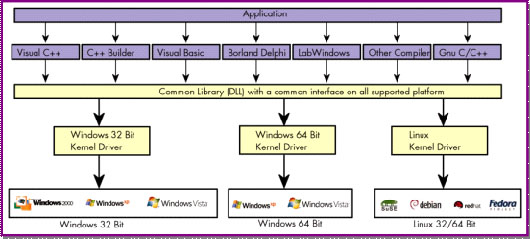

系統(tǒng)配套軟件:

系統(tǒng)軟件包括設(shè)備驅(qū)動(dòng)軟件,,二次開(kāi)發(fā)API函數(shù),以及FPGA開(kāi)發(fā)環(huán)境三部分,。

1.設(shè)備驅(qū)動(dòng)軟件和二次開(kāi)發(fā)API函數(shù):

我們提供豐富的接口函數(shù)和系統(tǒng)主要功能的例程,,支持C/C++,labview以及Matlab環(huán)境下的二次程序開(kāi)發(fā),。

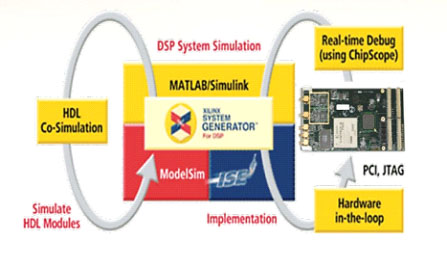

2.FPGA開(kāi)發(fā)環(huán)境:

我們提供采集模塊的全套FPGA開(kāi)發(fā)工程,,全部基于VerilogHDL或VHDL開(kāi)發(fā)環(huán)境。用戶(hù)邏輯只需要在目前已經(jīng)建立好的工程中加入自己的RTL代碼即可,。

同時(shí)提供Xilinx的systemgenerator同matlab/simulink接口工程和實(shí)例,。