熱搜關(guān)鍵詞: PCIe高速數(shù)據(jù)采集卡RFSOC高速數(shù)據(jù)采集軟件無(wú)線電平臺(tái)VPX高速數(shù)據(jù)采集卡高速信號(hào)采集卡PCIe數(shù)據(jù)采集數(shù)字信號(hào)處理

?

-

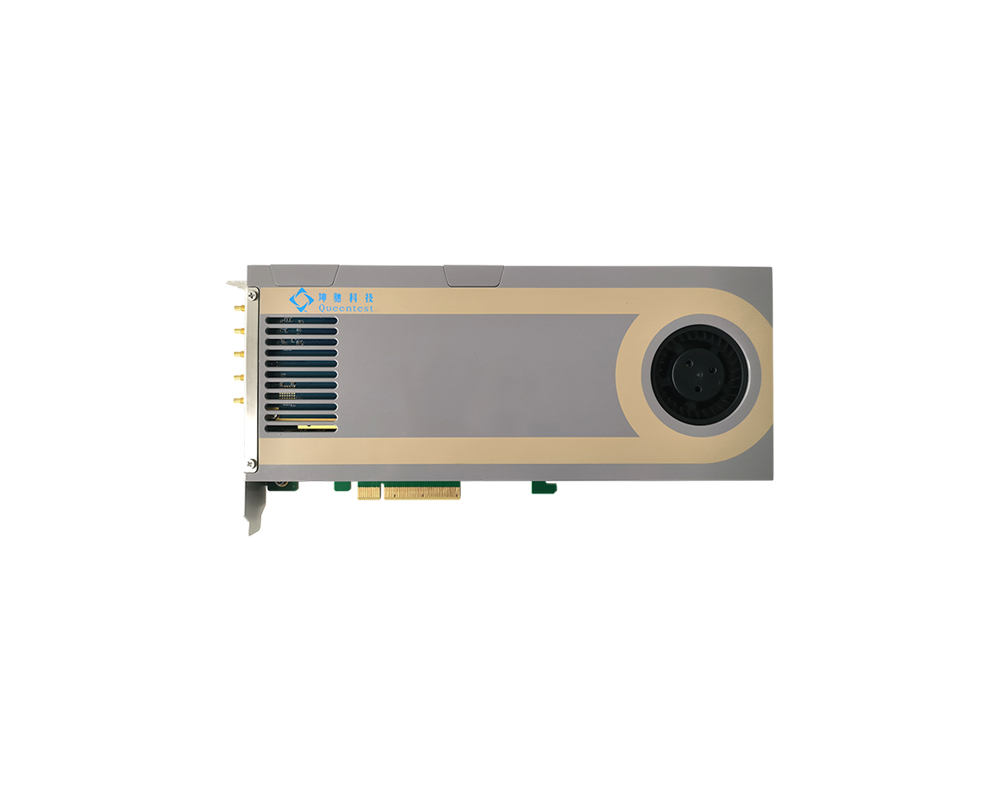

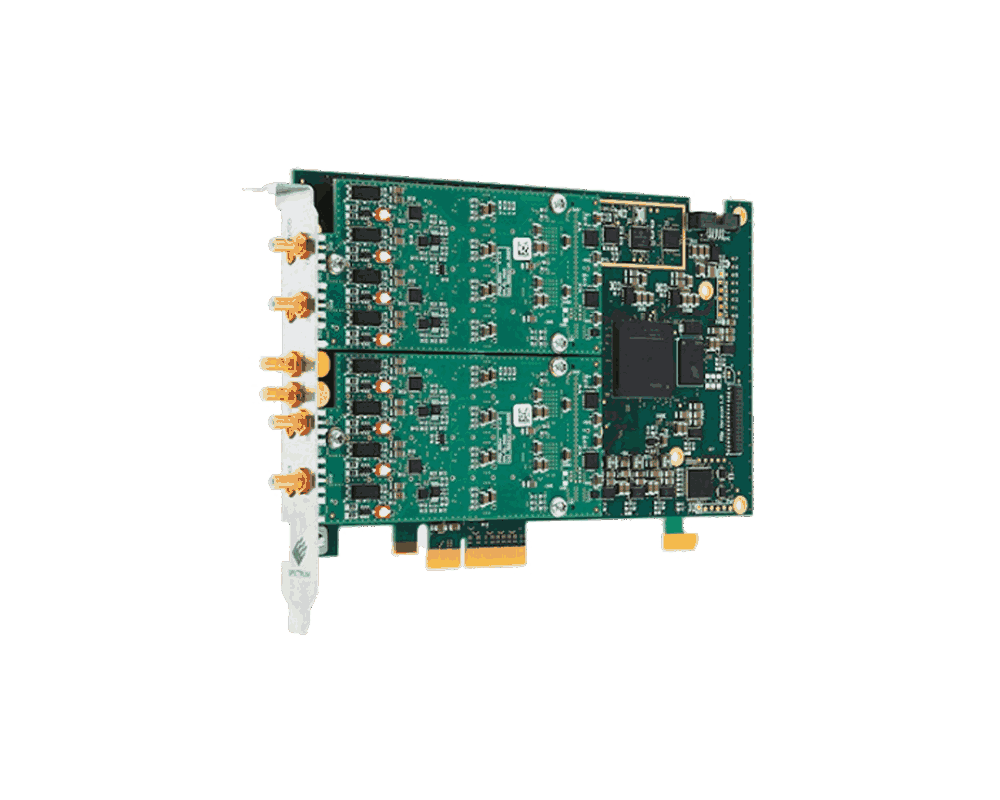

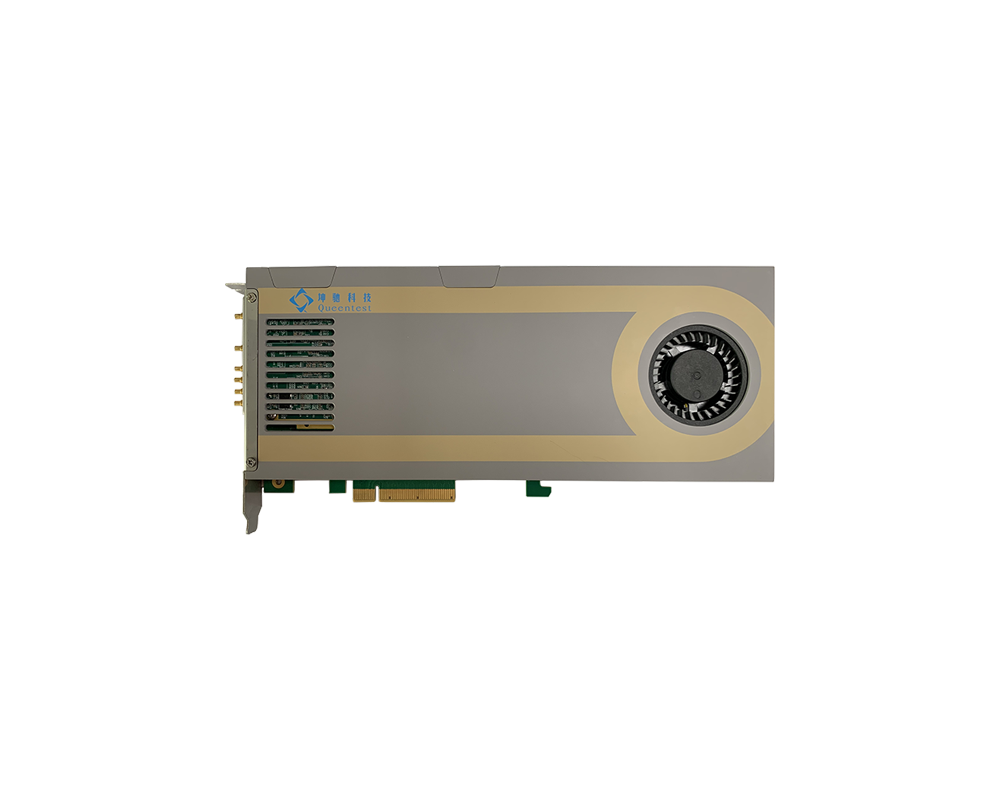

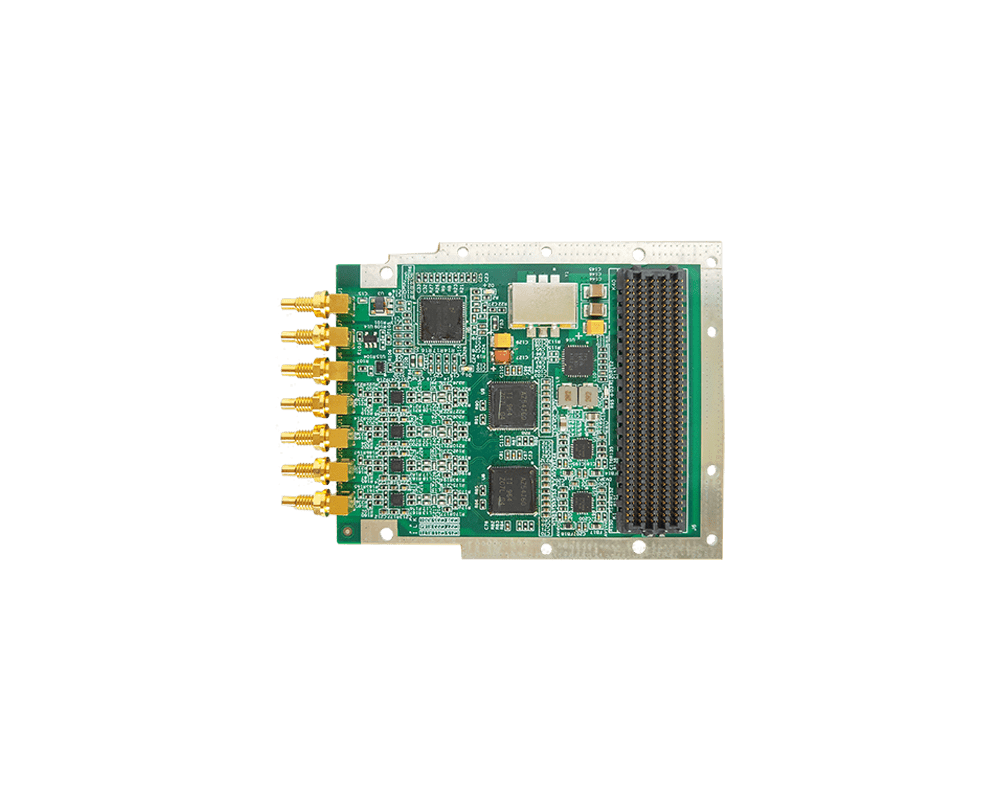

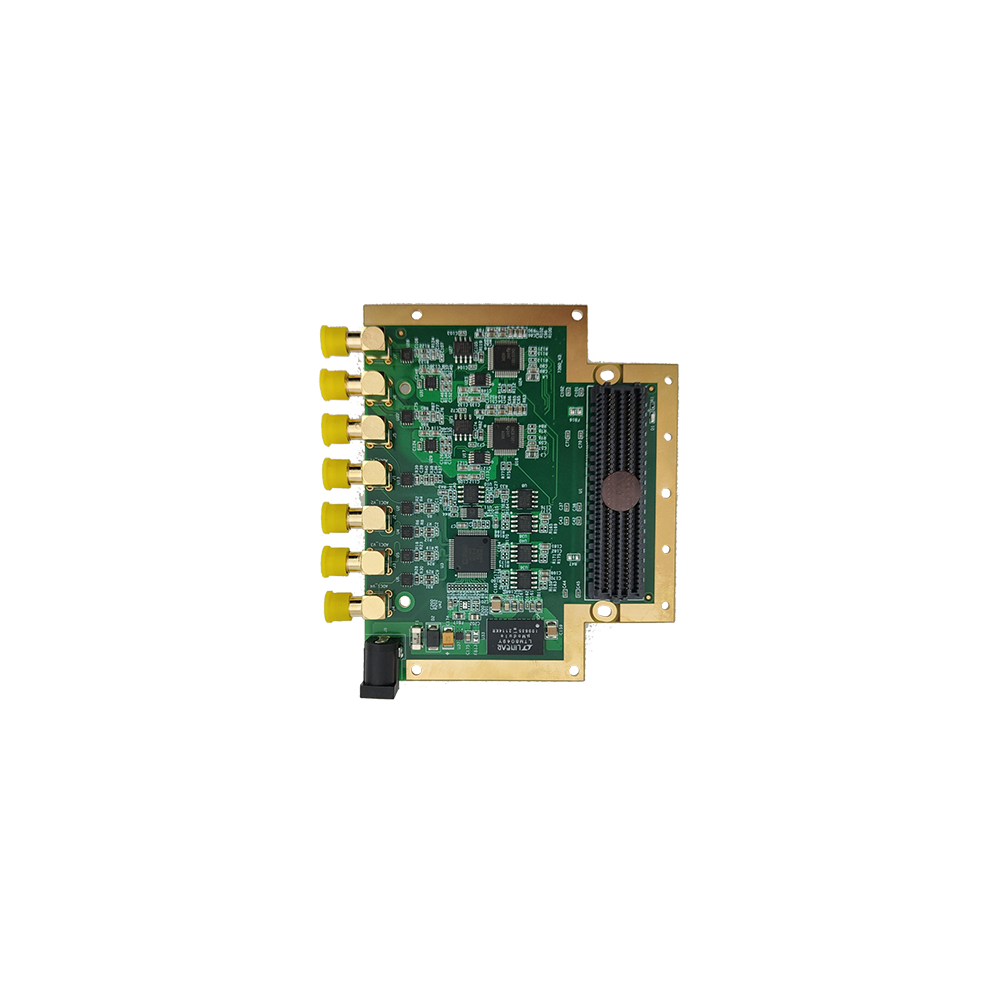

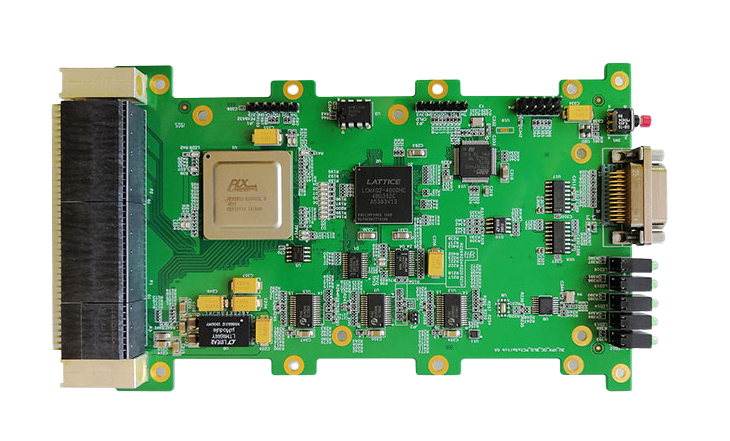

- QT7010-PCIe載板 總線:PCIe FMC數(shù)量類型:FMC

- QT7011-PCIe載板 總線:PCIe FMC數(shù)量類型:FMC+

- QT7012-PCIe載板 總線:PCIe FMC數(shù)量類型:FMC+

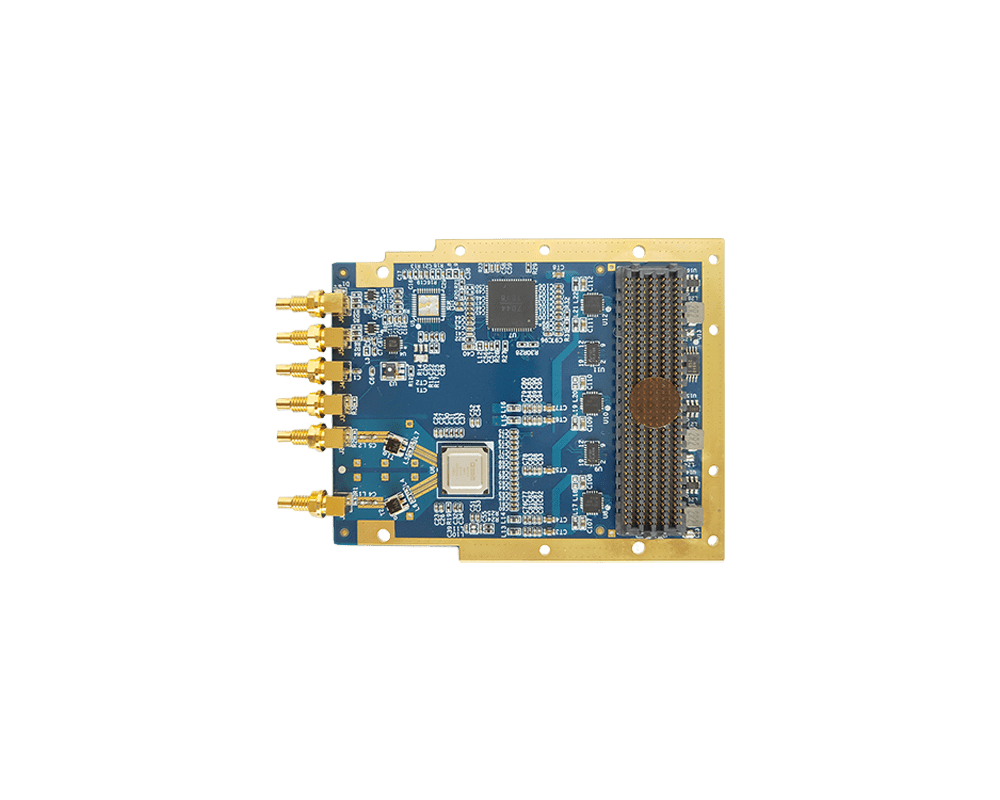

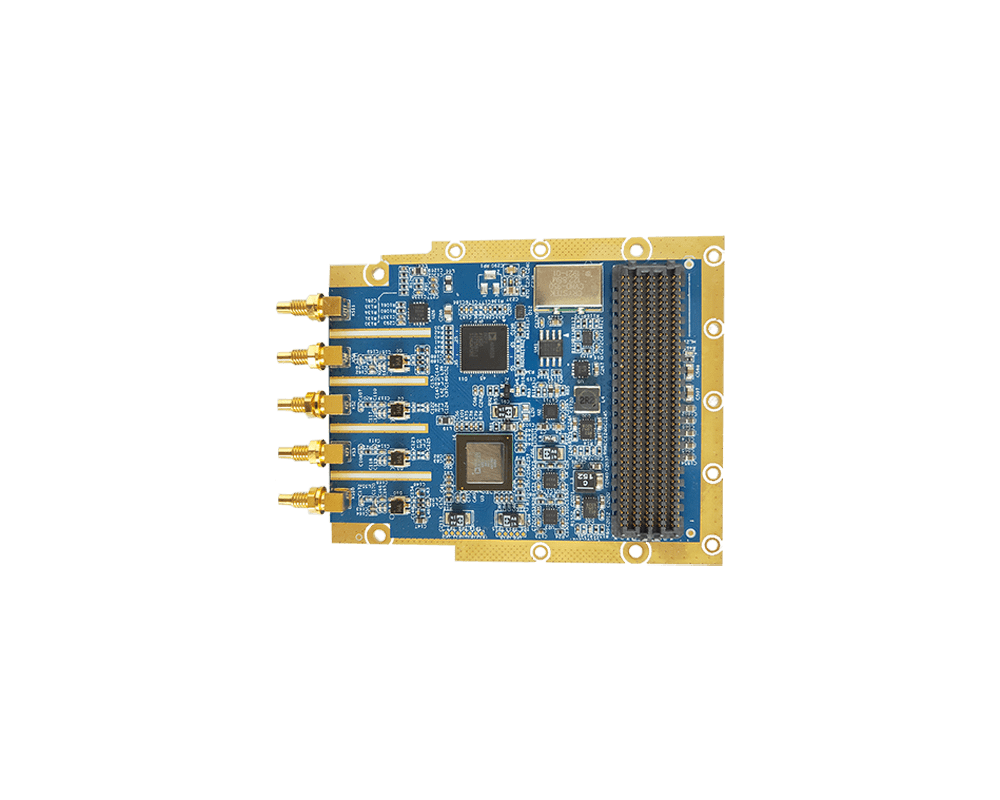

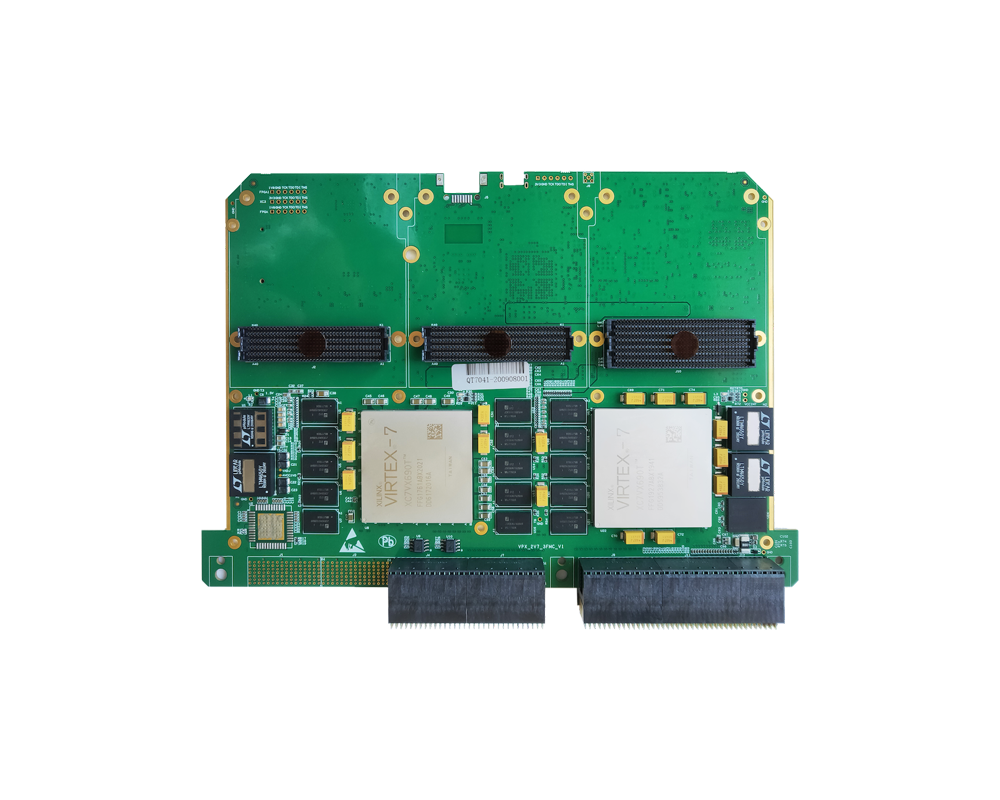

- QT7020-光纖/以太網(wǎng)載板 總線:光纖/以太網(wǎng) FPGA種類:XC7Z100FFG900(兼容045/035)

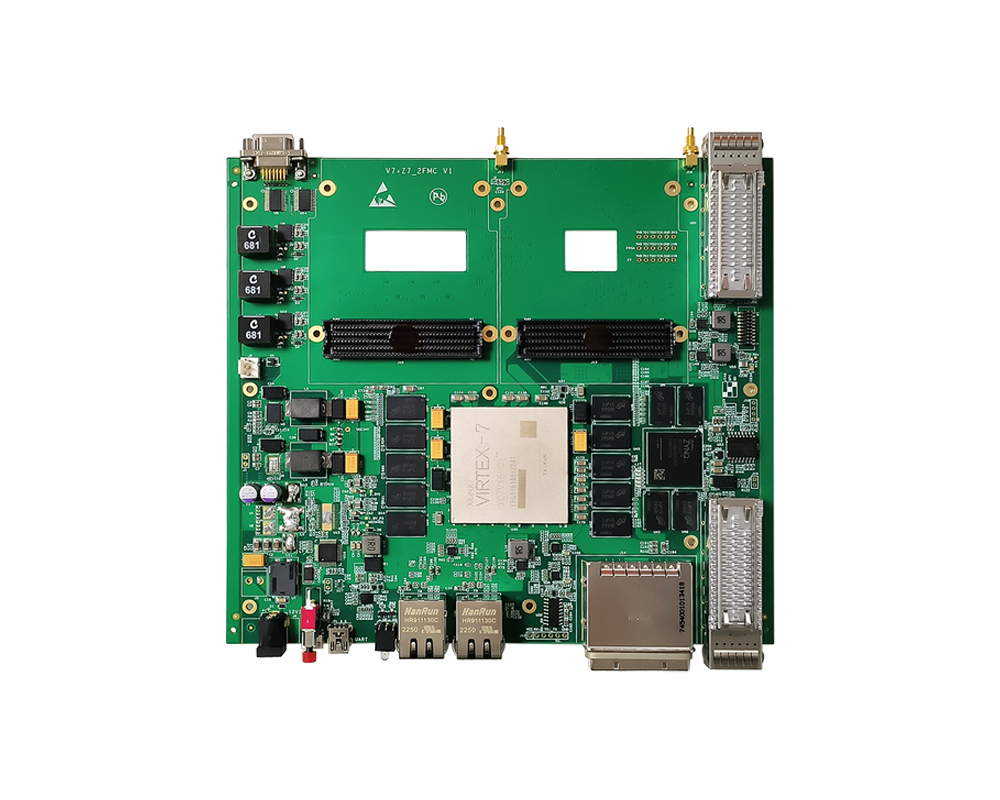

- QT7021-光纖/以太網(wǎng)載板 總線:光纖/以太網(wǎng) FPGA種類:XC7VX690TFFG1761

- QT7024-光纖/以太網(wǎng)載板 總線:光纖/以太網(wǎng) FPGA種類:XCZU19EG-2FFVC1760

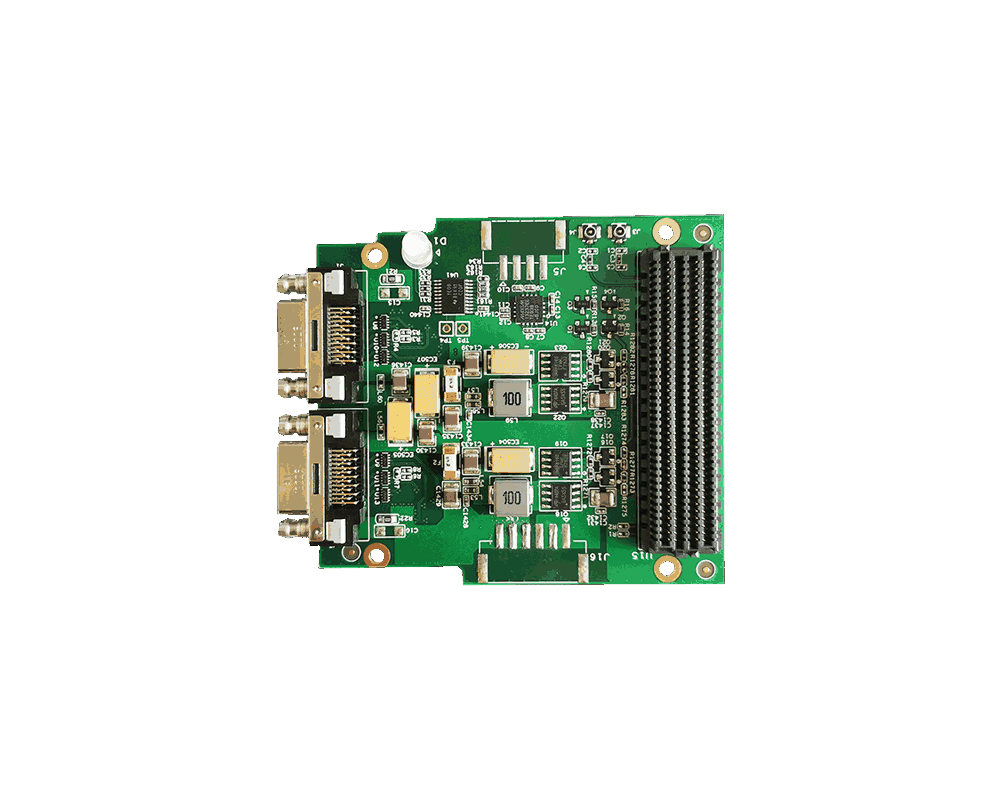

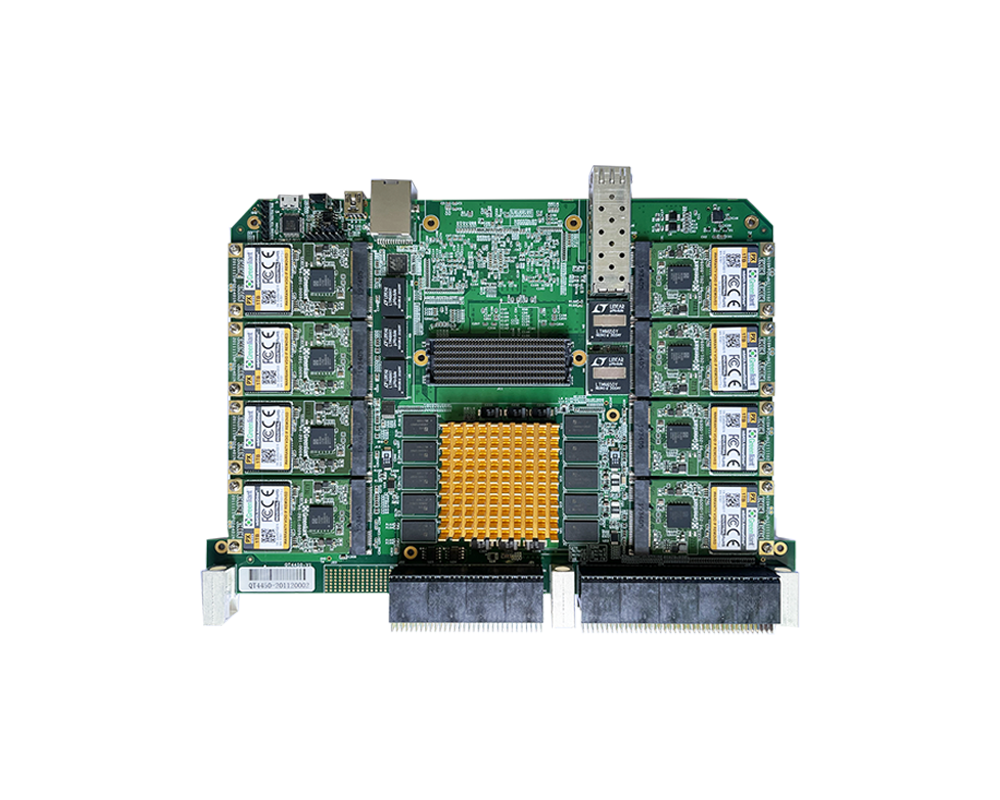

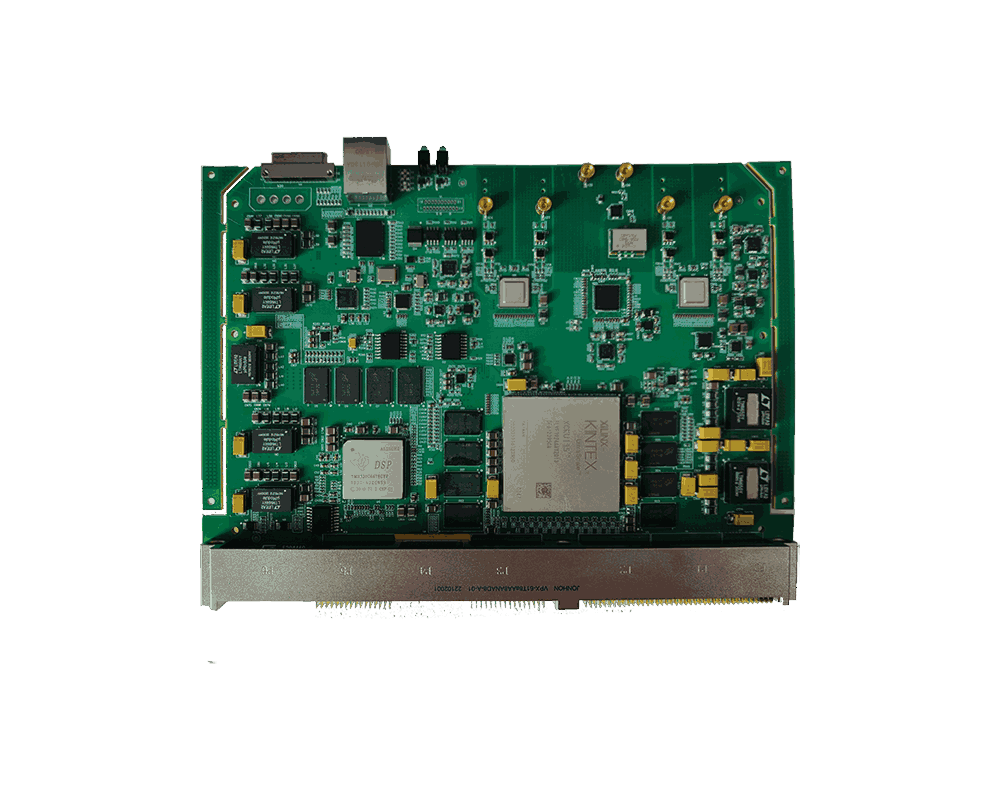

FPGA載板

-

- 射頻信號(hào)源-10 GHz丨SC5502A SC5503A 模塊類型:射頻信號(hào)源 輸入頻率:500MHz~10GHz

- 射頻信號(hào)模塊-6GHz丨SC5505A SC5506A 模塊類型:射頻信號(hào)源 輸入頻率:25MHz~6GHz

- 射頻信號(hào)源-20 GHz丨SC5510A SC5511A 模塊類型:射頻信號(hào)源 輸入頻率:100 MHz~20 GHz

- SC800 nanoSynth集成6 GHz SMT合成器 模塊類型:射頻信號(hào)源 輸入頻率:25MHz~6GHz

- 射頻信號(hào)源SC5520/SC5521 模塊類型:射頻信號(hào)源 輸入頻率:1 MHz-3.9 GHz

射頻信號(hào)源

-

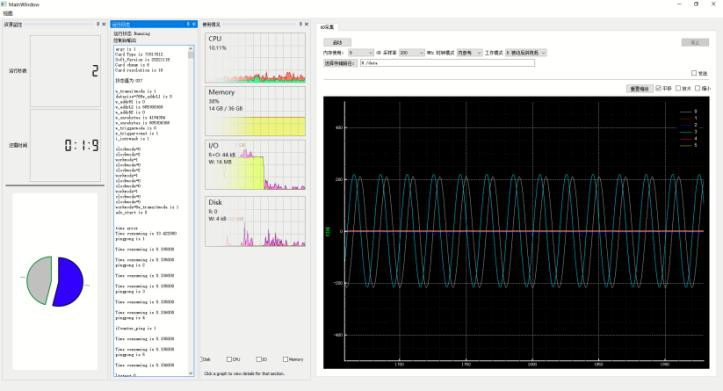

- 超聲應(yīng)用案例合集

- 聲場(chǎng)檢測(cè)系統(tǒng)

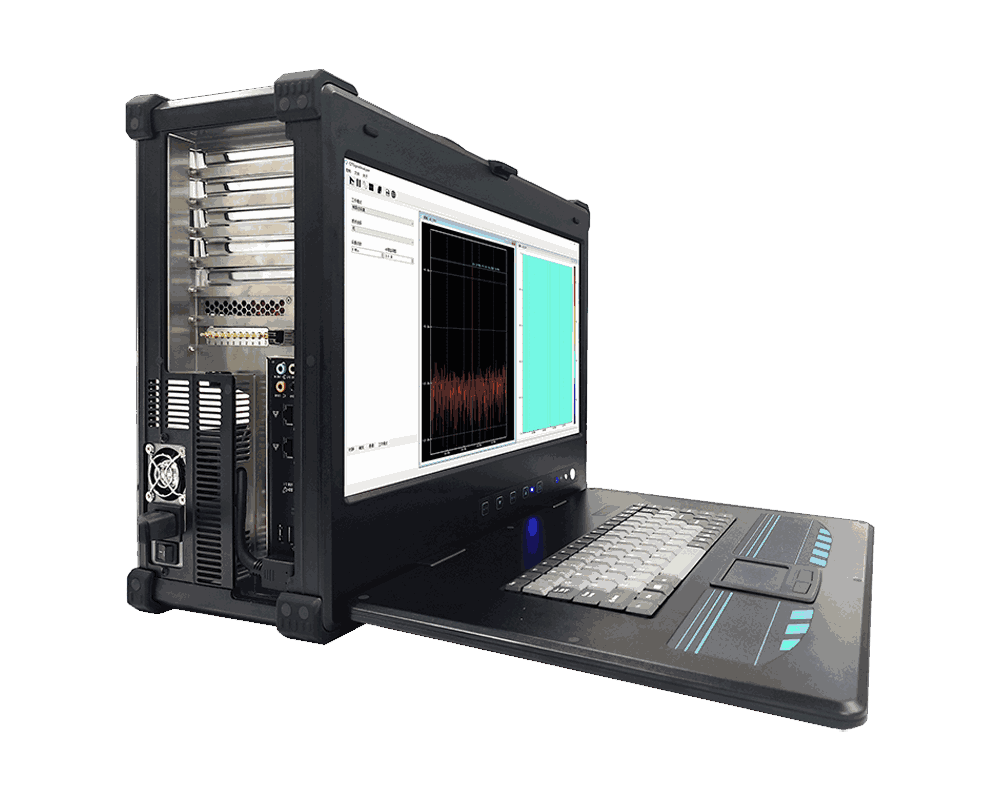

- 32路數(shù)據(jù)同步采集存儲(chǔ)系統(tǒng)

- 坤馳16通道USB超聲相控陣采集激勵(lì)系統(tǒng)

超聲類解決方案

-

- 激光雷達(dá)高速數(shù)據(jù)采集系統(tǒng)解決方案

- SAR回波模擬系統(tǒng)

- 雷達(dá)應(yīng)用合集

- IO大容量存儲(chǔ)系統(tǒng)

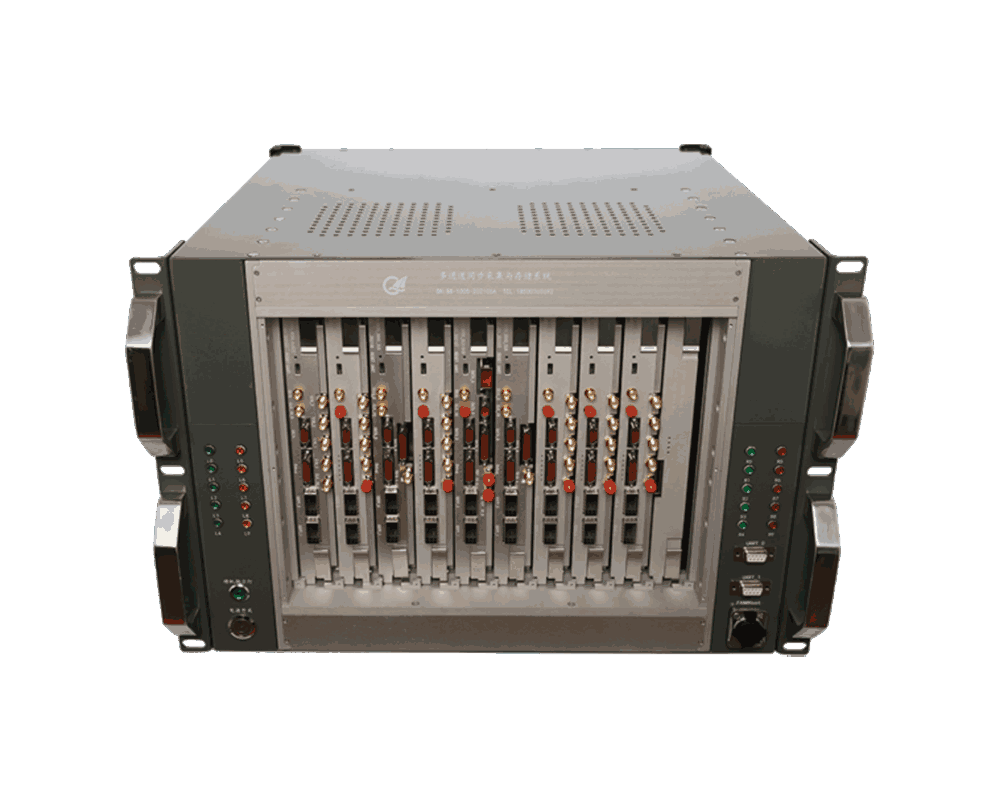

氣象雷達(dá)遙感探測(cè)

-

- 電力應(yīng)用合集

- 局放數(shù)據(jù)采集測(cè)試系統(tǒng)

- 基于以太網(wǎng)接口的電力局放采集系統(tǒng)

- UHF局部放電測(cè)試系統(tǒng)

電力類解決方案

-

- 衛(wèi)星激光測(cè)距高速數(shù)據(jù)處理解決方案

- 2G脈沖采集系統(tǒng)

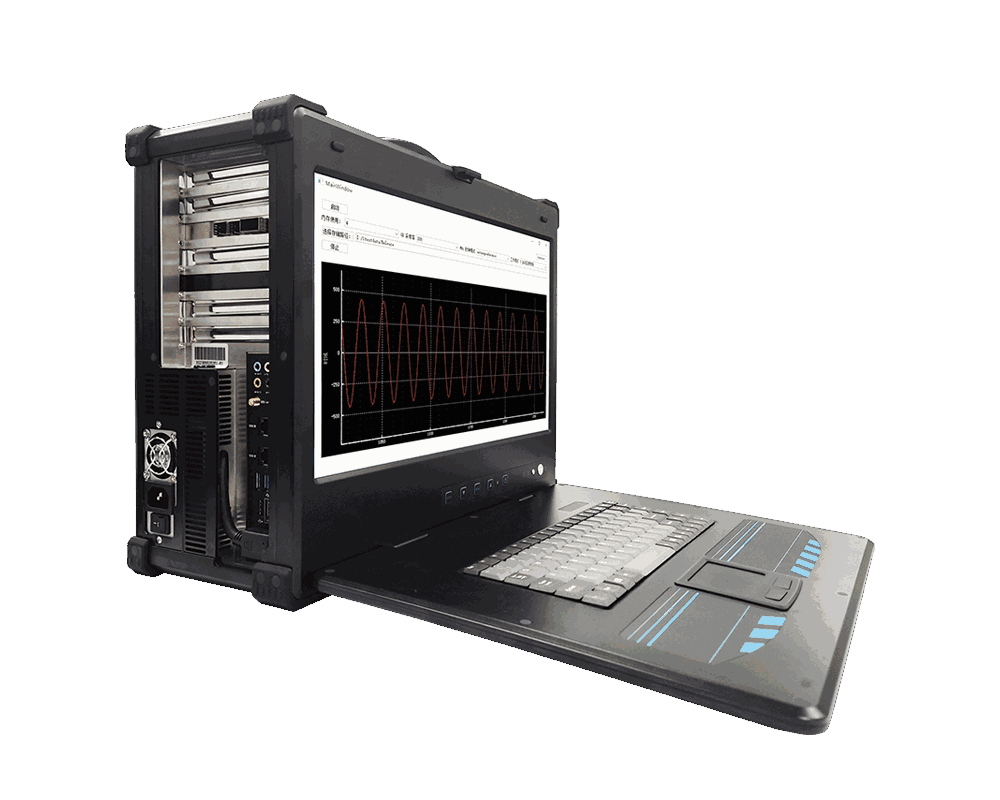

- 5Gsps雙通道信號(hào)采集系統(tǒng)實(shí)現(xiàn)

- 5G采集存儲(chǔ)系統(tǒng)