熱搜關鍵詞: 高速AD卡FMC子卡高速數(shù)據(jù)采集系統(tǒng)軟件無線電平臺VPX高速數(shù)據(jù)采集卡高速信號采集卡PCIe高速數(shù)據(jù)采集卡RFSOC

.png)

碼上聯(lián)系

碼上聯(lián)系

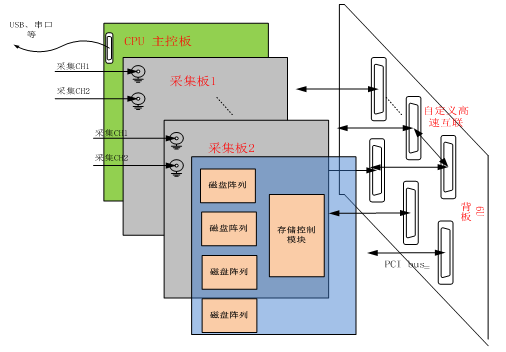

系統(tǒng)采用6U cPCI架構,包括如下幾個部分:

采集系統(tǒng):

1 采集模塊,,集成2通10bit 2.5GSPS ADC,,標準CPCI 6U卡尺寸,;

2. 時鐘,觸發(fā)可以同步,,可組成多通道采集系統(tǒng),,2個采集模塊可以組成4通道2.5Gsps同步采集系統(tǒng),;

3. 模擬前端AC藕合可選,50歐姆輸入,,AC輸入帶寬4.5MHZ~3GHz,,大500mVpp輸入,;

4. 板載校準信號源,,支持交錯采集自校準,;

5. 每塊采集模塊大支持板載2GB內存,,4通道系統(tǒng)總共4GB內存,;

6. 系統(tǒng)中的模塊均具備大規(guī)模FPGA,用戶可以方便的將自有的邏輯加入系統(tǒng)中,進行實時信號處理,;

7. 板載超低相位噪聲恒溫晶體為參考時鐘,,超低抖動時鐘發(fā)生器產(chǎn)生采集時鐘,;

8. 支持外觸發(fā)和外同步輸入,;

9. 支持標準32bit PCI總線,,采用DMA機制同計算機進行數(shù)據(jù)交換;

10. 自定義高速SRIO同存儲板互聯(lián),;

11. 板載溫度監(jiān)控系統(tǒng),;

12. 提供豐富的二次開發(fā)軟件和接口API函數(shù),,支持C/C++環(huán)境下的二次開發(fā),;

13. 整板采用導熱結構,模擬電路和時鐘電路全封閉屏蔽,。

高速存儲模塊:

1.板載高速存儲系統(tǒng),,支持8塊SSD盤并行存儲,,存儲速度大于1.2GB/s,;容量支持320GB到4TB,。

2.高速SRIO數(shù)據(jù)輸入輸出通道,支持2.5Gbps 數(shù)據(jù)收發(fā),。

3.采用加固結構,,SSD能牢靠的固定在載板上。

4.低功耗設計,,每個采集模塊全速工作,,包括8塊SSD硬盤,,功耗小于40W,。

機箱以及控制系統(tǒng):

1.標準6U 7槽 CPCI 系統(tǒng),,包括6U 7槽背板,,控制器以及機箱,可安裝上19寸機架,。

2.包括控制器模塊,、2個采集模塊,、1個高速存儲器模塊,。

3.系統(tǒng)支持單28V供電。

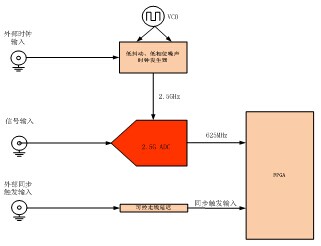

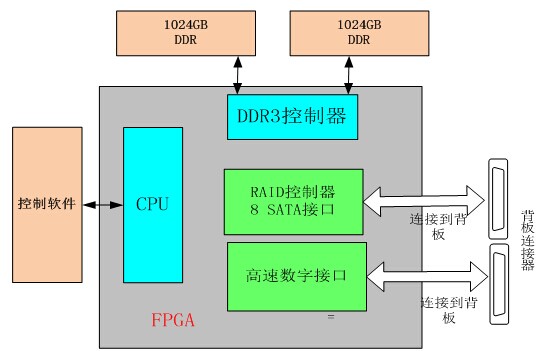

系統(tǒng)實現(xiàn)框圖如下:

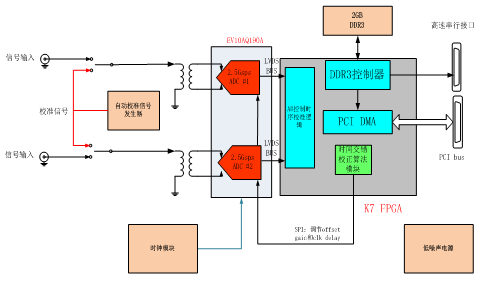

采集模塊的實現(xiàn):

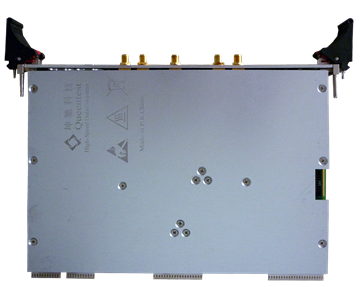

采集板卡外觀圖如下:

采集模塊采用1片雙通道2.5GSPS ADC 10bit,,每通道配置1GB的板載內存,,總共2GB,。如果采用10bit存儲模式,每通道可以分配到512Msample的內存大小,,8bit采集模式下每通道1Gsample。

每個通道配備獨立的信號調理和校準電路,,支持大輸入+/-500mV/AC信號,50歐姆輸入阻抗,。

采用Xilinx K7大規(guī)模FPGA,,支持用戶自定義開發(fā)FPGA邏輯,。

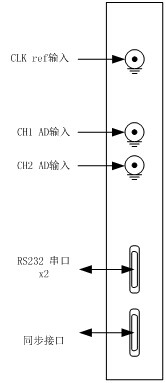

輸入輸出接口:

1. 外部參考時鐘輸入:SMA接口,,50歐姆單端輸入,,交流耦合,。輸入?yún)⒖紩r鐘頻率10MHz~100MHz;

輸入功率0dBm到9dBm,。

2. 模擬輸入信號,CH1 CH2: SMA接口,,50歐姆單端輸入,交流耦合,。輸入帶寬4.5MHz~3GHz(-3dB),;大輸入電壓500mVpp。

3. RS232串口,,micro-D接口,具備雙路RX TX通道,。

4. 同步接口,,micro-D接口,一路RS232協(xié)議接口,,秒沖輸入端(LVTTL),,觸發(fā)輸入端(LVTTL),,hold 輸出端(LVTTL)。

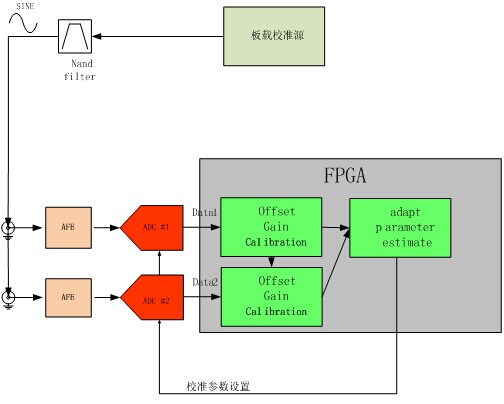

交錯采集動態(tài)校準:

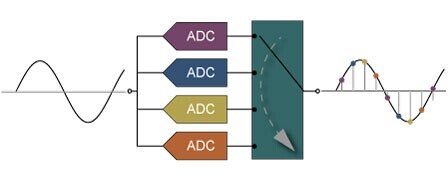

2.5Gsps是由2個1.25Gsps的 ADC采用時間交錯的算法組成的采樣系統(tǒng),。這就需要板載校準源在系統(tǒng)初始化以及溫度發(fā)生變化時進行校準,。

ADC的時間交錯采樣是一種并行使用多個ADC從整體上提高系統(tǒng)采樣率的方法。目前的挑戰(zhàn)是處理獨立的ADC通道之間的不匹配,,特別是在較高的頻率下,。

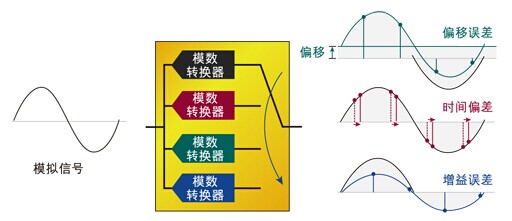

時間交替的主要難點是通道間采樣時鐘邊沿的精確校準和IC間固有變化的補償,。精確匹配各單獨模擬數(shù)據(jù)轉換器間的增益、偏移和時鐘相位是一項很大的挑戰(zhàn),,主要因為這些參數(shù)都取決于頻率。除非能夠實現(xiàn)這些參數(shù)的精確匹配,,否則動態(tài)性能和分辨率將會降低,。下圖顯示了三個主要誤差源,。

坤馳科技開發(fā)的時間交錯采樣校準算法能持續(xù)提供模數(shù)轉換器的增益,、偏移和時間偏差誤差的后臺估計值,,此算法對于校正靜態(tài)和動態(tài)失配誤差很有效,。 時間交錯采樣校準估計誤差,,并使用抑制的全部失配誤差重新構建信號,。誤差校正算法對于任何輸入信號類型均有效,。

校準系統(tǒng)實現(xiàn)方案

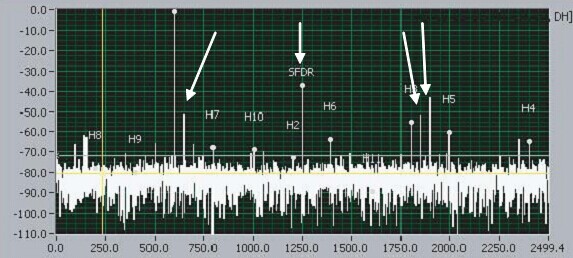

校準前的頻譜:

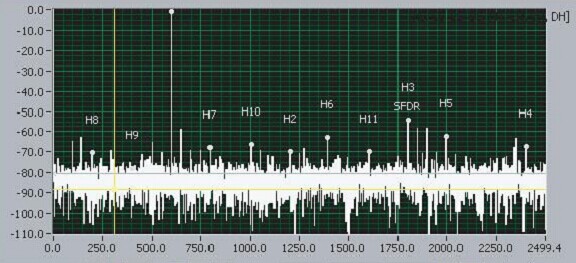

校準后的頻譜:

性能測試結果:

|

輸入信號頻率(MHz) |

ENOB(bit) |

SFDR(dB) |

|

100 |

8.3 |

-62 |

|

250 |

8.2 |

-60 |

|

500 |

8 |

-57 |

|

1000 |

7.5 |

-54 |

測試條件: 采樣率2.5Gsps,內部時鐘,。輸入信號85%FS,,外接帶通濾波器。

8192點FFT,,卷積Hanning窗,。

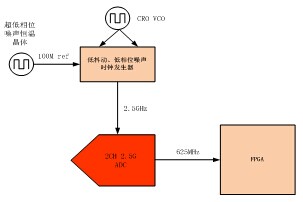

采集時鐘發(fā)生器:

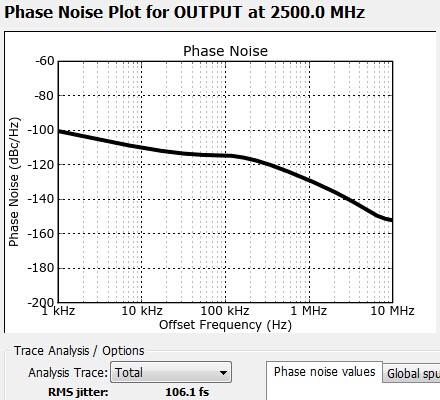

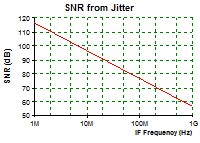

采集時鐘抖動對采集系統(tǒng)信噪比的影響:

2.5Gsps ADC 要求輸入2.5G時鐘的抖動小于150fs RMS,。

我們通過小型化的恒溫晶體加超低相位噪聲時鐘發(fā)生器,,實現(xiàn)2.5G時鐘輸出時的抖動約100fs rms

抖動對輸入信號的噪聲影響,。

高速ADC-FPGA數(shù)字接口校準:

每個LVDS對數(shù)據(jù)率為1.25Gbps,隨路時鐘為625MHz,。這個傳輸速度已經(jīng)使FPGA內部時鐘延遲大于數(shù)據(jù)延遲,,加上FPGA內部傳輸skew,,后果是每一路LVDS不一定同隨路時鐘對齊,。所以需要采用動態(tài)時間窗口調整狀態(tài)機,進行ADC LVDS輸入時序調整,,進行:

l 自動搜索數(shù)據(jù)窗口,,進行動態(tài)bit對齊,。

l 根據(jù)測試序列,進行動態(tài)10bit 字對齊,,保證數(shù)據(jù)一致性,。

l 監(jiān)控系統(tǒng)溫度變化,實時進行窗口調節(jié),,保證時鐘在數(shù)據(jù)窗口中心位置,。

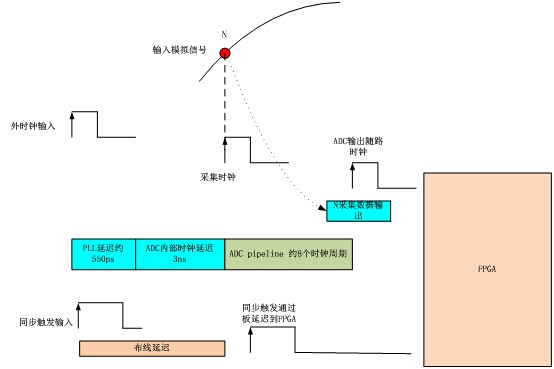

同步觸發(fā)和外參考時鐘的輸入方案:

延遲補償:

觸發(fā)信號相對時鐘的傳輸延遲(包括PLL延遲)可以通過PCB的走線進行大致的補償,,在FR4上,,延遲時間約為180ps/inch

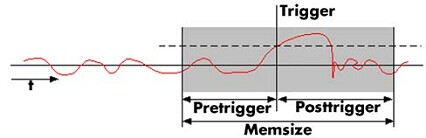

FPGA通過預觸發(fā)來補償ADC的pipeline 延遲:

邏輯允許設置一下參數(shù):

設置單次采集長度Mem-size;

設置觸發(fā)Pre-trigger點數(shù),;

Post-trigger=mem-size - Pre-trigger

觸發(fā)參數(shù):

Pre-trigger: 0~16k,。

Mem-size:8~1G。

Step: 8(?。?。

外觸發(fā)脈沖為LVTTL。

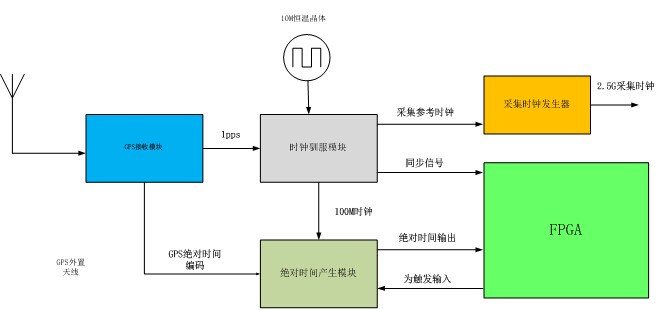

關于秒脈沖同步控制:

GPS同步模塊由以下部分組成:

l GPS接收模塊:輸出1pps秒脈沖,,目前精度30ns rms(1σ),。

l 本機恒溫晶體:輸出10MHz,頻率穩(wěn)定度1e-9(阿倫方差),。

l 時鐘馴服模塊:根據(jù)GPS輸出的1pps信號,,同步每個采集模塊的本地恒溫晶體;同時產(chǎn)生1s頻率的同步時鐘信號,。保障在GPS衛(wèi)星短時間失鎖情況下仍然能維持同步穩(wěn)定,。

l GPS絕對時間模塊:讀取GPS授時時間,同時使用同步的100M時鐘進行計數(shù),,產(chǎn)生本地20ns精度的絕對時間,。

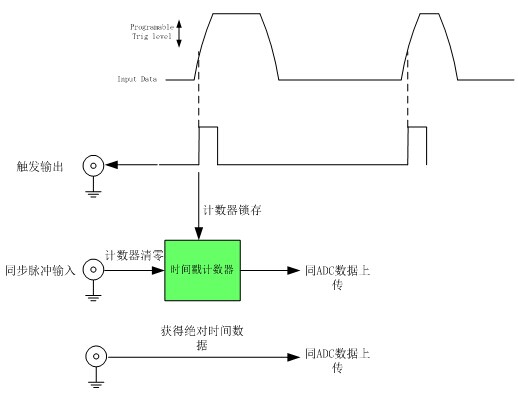

采集間模塊同步機制:

同步原理如下圖所示:

同步機制在采集模塊FPGA內實現(xiàn)。采用兩種方式實現(xiàn)同步:

l 時間戳模式: 驅動時鐘為采集時鐘,,頻率2.5GHz,,FPGA 5分頻處理,分辨率為2ns。當有觸發(fā)事件時,,鎖存時間戳計數(shù)器,,將該計數(shù)器值同ADC數(shù)據(jù)值上傳服務器。GPS同步模塊輸出的同步脈沖負責每秒為計數(shù)器清除一次,,

保證各個采集模塊的計數(shù)器同步,。如果各個采集模塊是同時滿足觸發(fā)條件的,此時各個通道的計數(shù)器值應該相等。

l 絕對時間記錄模式: 觸發(fā)脈沖輸出到GPS絕對時間計數(shù)器中,;當絕對時間計數(shù)器檢測到上升沿,,鎖定絕對時間計數(shù)器,然后通過總線形式讀取當前時間,,同ADC采集數(shù)據(jù)上傳主機,。

模塊間時間同步精度:

時間戳模式:根據(jù)GPS同步精度30ns rms(1σ)±2ns。

絕對時間記錄模式:根據(jù)GPS同步精度30ns rms(1σ)±20ns+傳輸skew,。

高速存儲系統(tǒng):

1.在1塊6U的標準插卡上集成了8個接口的SATA磁盤控制器,,本地支持2GB的讀寫緩存,能緩沖較長的數(shù)據(jù),,不至于因為某個磁盤突發(fā)響應緩慢而影響了整個系統(tǒng)的讀寫速度,。

2.采用嵌入式CPU,配合優(yōu)化的系統(tǒng)控制軟件,,大效率的執(zhí)行磁盤的管理,,回避了操作系統(tǒng)的延遲。

高速存儲模塊外形圖

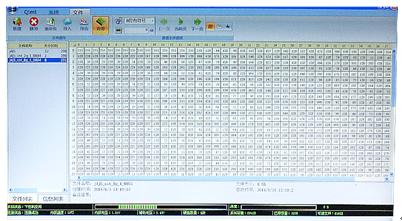

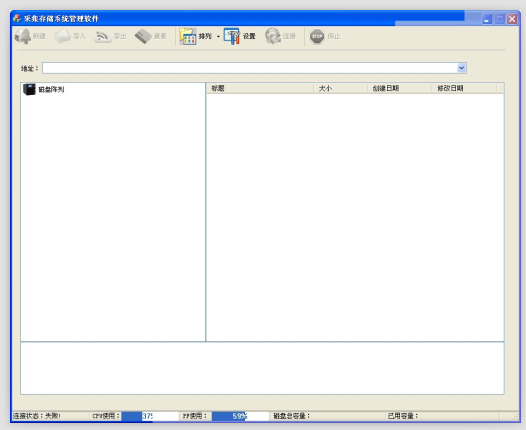

系統(tǒng)配套軟件:

控制軟件運行于Windows系統(tǒng),,提供人機交互圖形化界面,,通過串口通信控制存儲板和系統(tǒng),通過PCI接口與計算機交換批量數(shù)據(jù),。另外,,用戶也可以使用串口控制臺以命令行的模式對系統(tǒng)進行控制。

系統(tǒng)可提供的典型控制指令有:

ü 建立或刪除文件等操作

ü 指定數(shù)據(jù)存盤或讀出的文件地址,、大小

ü 選擇存盤數(shù)據(jù)來源,,例如選擇ADC或PCI主機作為數(shù)據(jù)源

ü 選擇存盤數(shù)據(jù)導出目的地,例如選擇DAC或PCI作為輸出

ü 啟動,、暫停,、停止數(shù)據(jù)存盤

ü 啟動、暫停,、停止數(shù)據(jù)導出

ü 以列表或圖形模式顯示存盤數(shù)據(jù)

ü 設置RAID模式

ü 顯示系統(tǒng)空間使用,、溫度、工作日志等信息

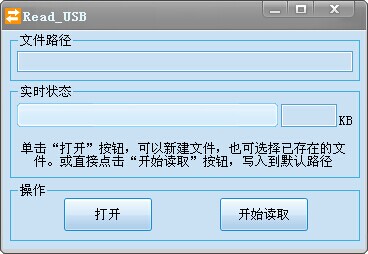

軟件交互界面如下:

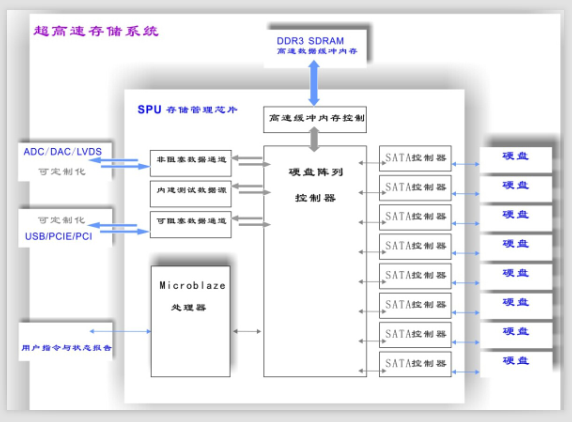

超高速存儲系統(tǒng)(Super Speed Storage System,,以下簡稱4S系統(tǒng))的核心技術要素是一顆專門為高速數(shù)據(jù)存儲,,特別是為適應模數(shù)、數(shù)模變換(ADC,、DAC)等連續(xù)強實時性數(shù)據(jù)流的存儲或回放而設計的專用芯片,。該芯片基于片上系統(tǒng)(System on chip,SOC)構架設計,并使用FPGA芯片實現(xiàn),在此將該芯片其命名為“存儲處理單元”(Storage Processing Unit,簡稱SPU),。

4S系統(tǒng)構架示意圖如下:

SPU芯片內部集成了多個SATA主控制器,,因此該芯片可以直接同時讀寫多個具備SATA接口的存儲設備,,例如常見的SATA接口硬盤。同時,,SPU內部設計了對多塊硬盤設備進行管理的邏輯系統(tǒng),即冗余磁盤陣列(RAID)管理系統(tǒng),。RAID管理系統(tǒng)通過多種可選擇的模式對多塊硬盤進行靈活管理,,使得整個4S系統(tǒng)的數(shù)據(jù)吞吐能力得到提升。SPU芯片內部集成了一個32位的通用處理器(CPU),,該CPU用于整個存儲系統(tǒng)的管理,,包括對單個SATA接口硬盤的管理,RAID管理,,還用于文件系統(tǒng)的實現(xiàn),,與用戶指令信息交互的實現(xiàn),數(shù)據(jù)輸入輸出通道的選擇和控制等,。為了實現(xiàn)強實時數(shù)據(jù)流的讀寫,,本系統(tǒng)采用了我公司專門設計的快速存儲文件系統(tǒng)(Fast Storage File System,FSFS),該文件系統(tǒng)使得每個存盤文件占用的是硬盤上連續(xù)的物理地址空間,,同時存盤或回放數(shù)據(jù)流通過系統(tǒng)內專門設計的DMA控制器寫入硬盤,,并不使用CPU進行數(shù)據(jù)搬移。通過FS文件系統(tǒng)和DMA控制器的實現(xiàn),,使得4S系統(tǒng)可以具備特別優(yōu)異的存儲帶寬,。SPU芯片對外提供多個數(shù)據(jù)輸入輸出通道,通過與各種貨架化的,、或者為用戶定制化的接口電路配合,,使得4S系統(tǒng)可以靈活地進行數(shù)據(jù)的存儲、回放或轉存,。

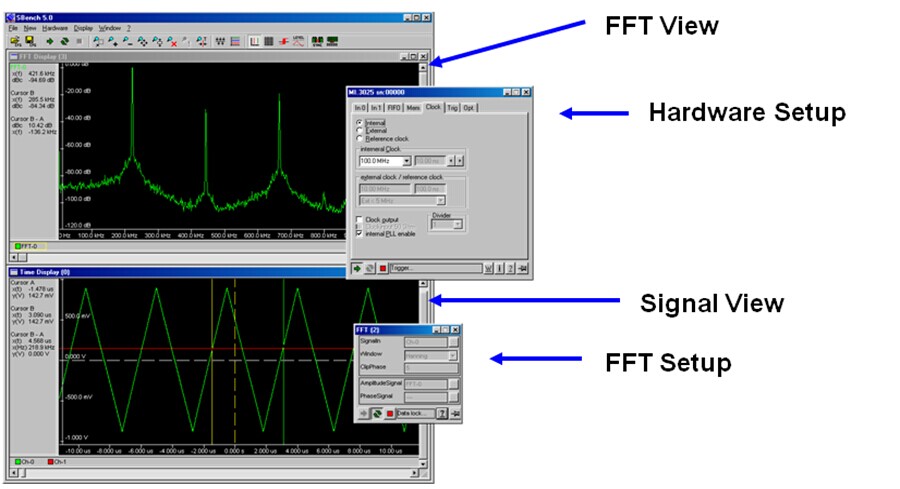

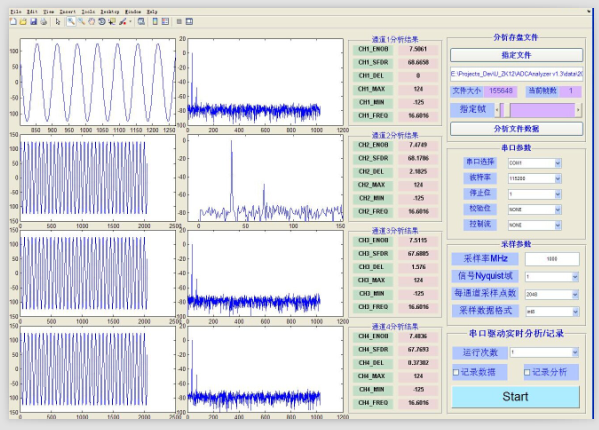

波形監(jiān)控軟件(虛擬示波器軟件)

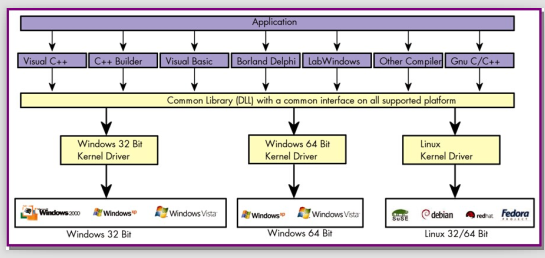

系統(tǒng)軟件包括應用軟件,,二次開發(fā)API函數(shù),以及FPGA開發(fā)環(huán)境三部分,。

1.應用軟件,,具有虛擬示波器功能,方便設置硬件,,讀取/保存數(shù)據(jù)以及波形顯示/頻譜分析功能,。

其功能和界面如下所示:

2.二次開發(fā)API函數(shù):

我們提供豐富的接口函數(shù)和系統(tǒng)主要功能的例程,支持C/C++環(huán)境下的二次程序開發(fā),。

該系統(tǒng)為用戶提供了兩種控制方法,。一種是通過串口控制臺,以命令行的形式控制并監(jiān)測系統(tǒng),;另一種是通過運行于Windows系統(tǒng)的圖形化界面控制并監(jiān)測系統(tǒng),。串口控制臺通過RS232串口與4S系統(tǒng)通信,,具備簡潔直接的優(yōu)點,并支持完整的控制和調試指令,,缺點是界面友好性略差,,而圖形化界面則具備良好的交互友好性。另外,,4S系統(tǒng)提供USB,,光纖或者PCIE等接口方式用于存儲數(shù)據(jù)的高速導入導出,具體使用哪一種通道方式可根據(jù)用戶的需求配置,。

無論是串口控制臺還是圖形化軟件界面,,都支持各項主要功能,例如:創(chuàng)建或刪除文件等FS文件系統(tǒng)支持的操作,,使用某一個輸入輸出通道(例如集成有AD/DA電路FMC子板)寫文件或導出文件,,查看系統(tǒng)信息,查看文件數(shù)據(jù)片段等等,。另外,,串口控制臺還提供了一些高級的調試功能,例如:直接讀寫硬盤物理地址,,設置系統(tǒng)內某些外圍芯片(例如設置時鐘芯片從而調整信號采樣率)等等,。圖形化軟件界面則還可以提供以圖形化模式顯示文件數(shù)據(jù)片段等功能。

FS文件系統(tǒng)的使用與常見的NTFS等文件系統(tǒng)有所不同,,FS文件系統(tǒng)需要先建立一個固定大小的文件,,然后對文件進行讀寫操作,包括覆蓋式的寫操作,,也就是FS文件系統(tǒng)不支持文件大小的動態(tài)變化,,對系統(tǒng)的讀寫操作都是以某一個已經(jīng)建立的文件為對象的。當然,,對某一文件所進行的讀寫操作的大小可以小于文件自身的大小,。例如,如果某一個文件大小為100G字節(jié),,那么可以對其中任意的10GB進行寫入覆蓋或導出操作,。

這里簡略介紹串口控制臺的使用方法。例如,,用戶需要存儲10GB的ADC采樣數(shù)據(jù)然后使用DAC回放所記錄的10GB數(shù)據(jù),,那么需要首先建立一個10GB大小的文件或者使用已經(jīng)存在的文件,然后啟動存儲,,等待存儲完成后啟動回放操作,。這個過程可能涉及使用的指令流程是:

輸入

輸入

輸入

如果使用圖形化界面,,那么整個操作流程是類似的,只需按照圖形界面的文字提示信息操作即可,。

在此以一種典型的使用過程為例,,說明系統(tǒng)使用方法。

假設我們的目的是通過ADC采樣并記錄量化后的數(shù)據(jù),,然后再通過DAC重構模擬信號或者通過USB將數(shù)據(jù)導入通用計算機,,那么主要操作過程如下。

1. 連接系統(tǒng)硬件,,主要包括:連接模擬信號至FMC子板上的ADC信號接口,;將計算機串口和USB接口連接至后IO板上的相應接口;連接機箱電源,。

2. 打開電源,,并等待大約10秒鐘,當看到存儲板前面板指示燈閃爍,,說明硬件已啟動完成,。

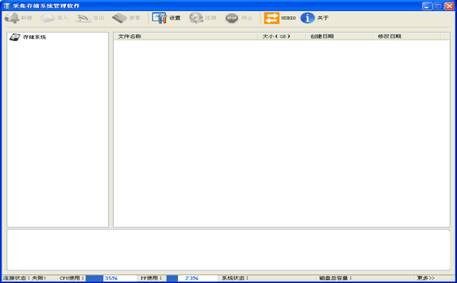

3. 在計算機上打開已事先安裝好的“采集存儲系統(tǒng)管理軟件”,看到如下界面:

4.點擊“設置”進行串口設置,。根據(jù)計算機上實際使用的串口選擇串口端口號,,其它參數(shù)使用默認值。

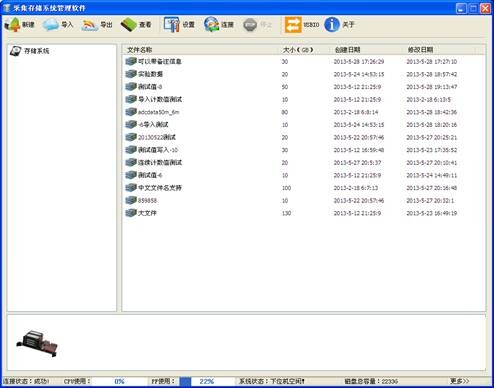

5.如果設置正確,,軟件界面上的“連接”按鈕點亮,。點擊“連接”,軟件將會列出系統(tǒng)內已存在的文件名稱,、文件大小,、創(chuàng)建時間、修改時間等信息,,點擊相應的列首可以改變文件排序方法,。如下圖:

需要說明的是,,本系統(tǒng)中文件的大小需要在創(chuàng)建時固定,以后不能更改,。文件名長63字節(jié),,并支持255字節(jié)的文件備注信息。

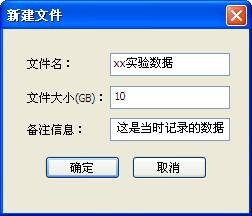

6.在此創(chuàng)建一個10G字節(jié)的文件,,可以點擊“新建”按鈕,,也可以在文件區(qū)域右鍵選擇新建,然后彈出如下窗口:

在上面的窗口中輸入文件名稱,、文件大小,、以及可選擇輸入或不輸入的備注信息,點擊確定按鈕,,文件創(chuàng)建完成,。如下圖:

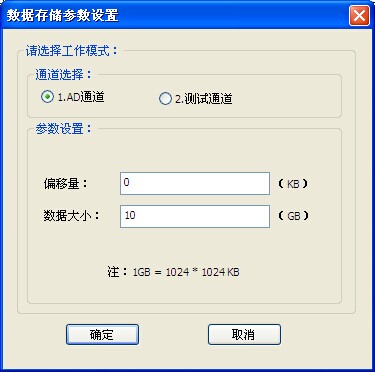

7. 現(xiàn)在使用新建的文件作為存儲空間,存儲ADC采樣數(shù)據(jù),。首先點擊該文件,,然后點擊“導入”按鈕,彈出如下對話框:

上面對話框中,,“偏移量”用于指定數(shù)據(jù)存盤時在該文件空間中的起始位置,,“數(shù)據(jù)大小”用于指定需要存儲的數(shù)據(jù)量,這兩者之和不能大于文件自身的大小,。

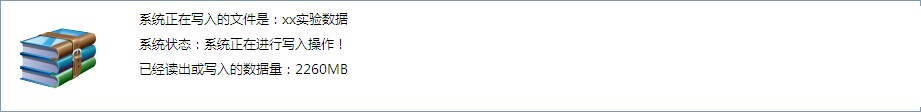

設置好參數(shù)后,,點擊確定,系統(tǒng)開始使用ADC采集模擬信號并將采樣數(shù)據(jù)存儲到指定的文件空間,。此時通過軟件下方的信息框,,用戶可以看到已存盤的數(shù)據(jù)量,如下圖:

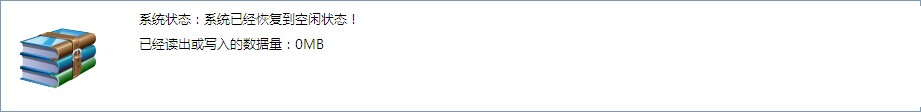

用戶可以點擊“停止”按鈕強制停止數(shù)據(jù)存儲,,也可以等待存儲完成后軟件自動停止,。如果采樣停止,信息框提示如下:

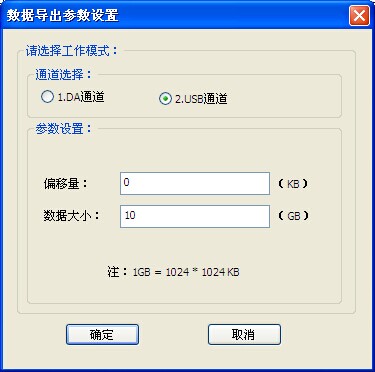

8. 現(xiàn)在通過USB將數(shù)據(jù)導出至計算機,。首先點擊剛才新建的文件,,然后點擊“導出”按鈕,彈出如下對話框:

如果選擇“DA通道”,,那么采樣數(shù)據(jù)將驅動DAC芯片重構模擬信號,。在此選擇“USB”通道,并點擊確定,。此時系統(tǒng)已開始從硬盤讀出數(shù)據(jù)并等待USB讀取,。

如果用戶點擊“停止”按鈕,可以強制停止導出,。

9. 點擊“USBIO”按鈕,,彈出如下軟件界面:

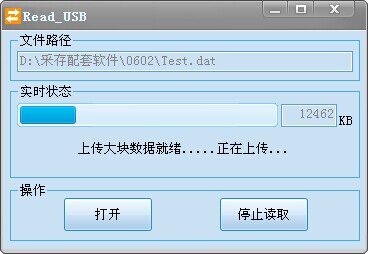

通過“打開”按鈕指定計算機上的文件路徑和名稱,,從系統(tǒng)導出的數(shù)據(jù)將寫入指定的文件。點擊“開始讀取”按鈕,,數(shù)據(jù)開始從系統(tǒng)導出并寫入計算機,,此時軟件實時顯示已讀出的數(shù)據(jù)量:

點擊“停止讀取”則寫文件結束。此后如果再點擊“打開”,可以指定新的文件,,并可以將后續(xù)導出的數(shù)據(jù)寫入新的文件,。

此時數(shù)據(jù)已導出至計算機,并以二進制格式存儲,,用戶可以通過自己設計的軟件分析數(shù)據(jù),。例如,使用我公司的一款ADC分析軟件讀取存盤文件,,可以得到ADC采樣數(shù)據(jù)的一些相關信息:

10. 另外,,通過點擊軟件界面上的“關于”按鈕可以得到系統(tǒng)硬件的相關產(chǎn)品信息,點擊“更多”按鈕可以得到系統(tǒng)硬件的關鍵電壓,、溫度,、以及存儲系統(tǒng)使用情況等信息,,如下圖: