量子加密通信驗(yàn)證系統(tǒng)

1.概述:

項(xiàng)目背景:

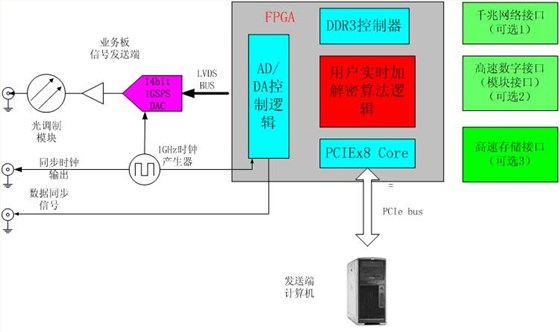

本系統(tǒng)通過基于PCIE總線的高速ADC采集和高速DAC回放系統(tǒng),實(shí)現(xiàn)量子加密通信中的實(shí)時(shí)大數(shù)據(jù)量傳輸、同步接收和量子加解密計(jì)算,。系統(tǒng)中高速信號發(fā)生與同步采集系統(tǒng)主要用于高速光調(diào)制信號的產(chǎn)生和在接受端進(jìn)行同步采集功能,。通過系統(tǒng)通過PCIEx8總線與計(jì)算機(jī)進(jìn)行通訊(或者通過單獨(dú)的數(shù)字IO),同時(shí)能將需要輸送到光調(diào)制模塊的數(shù)據(jù)實(shí)時(shí)的從計(jì)算機(jī)中傳輸?shù)焦庹{(diào)制模塊上,;同時(shí)在接收端同步采集光模塊的解調(diào)信號并將解調(diào)的數(shù)字信號傳輸進(jìn)計(jì)算機(jī)中。板載的FPGA可以進(jìn)行實(shí)時(shí)的高數(shù)據(jù)帶寬的量子加解密運(yùn)算,大大減輕計(jì)算機(jī)的負(fù)擔(dān),。

系統(tǒng)原理圖:

需要配圖

我們面臨的挑戰(zhàn):

1、量子加密通信采用光通信模式,,需要設(shè)計(jì)復(fù)雜的光電轉(zhuǎn)換設(shè)備,。

2、收、發(fā)數(shù)據(jù)兩端距離較遠(yuǎn),,需要解決遠(yuǎn)距離同步問題,。

3、加密算法數(shù)據(jù)量大,,且要求實(shí)時(shí)性,;FPGA并行算法開發(fā)復(fù)雜度較大。

4,、由于接收和發(fā)送均采用光脈沖信號,,這就需要特殊設(shè)計(jì)ADC的前端放大器,和DAC的輸出驅(qū)動(dòng)器,。

5,、高速ADC和DAC芯片時(shí)鐘速度快,數(shù)據(jù)線多,,對FPGA接口的時(shí)序要求非常嚴(yán)格,。

解決方案:

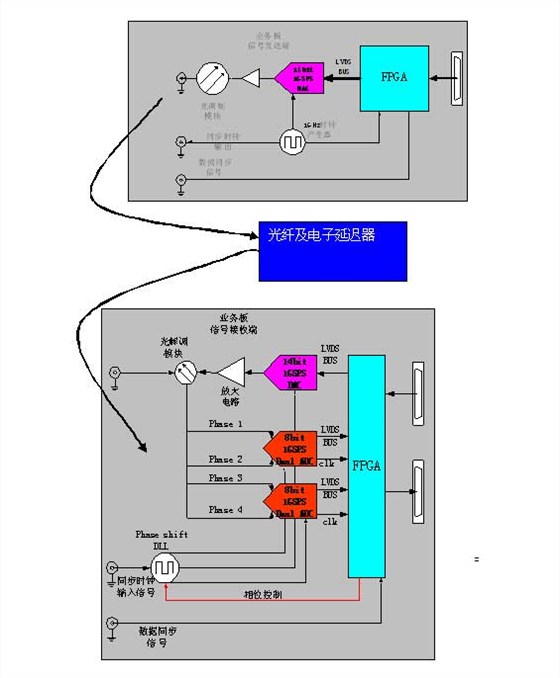

整個(gè)系統(tǒng)由自行開發(fā)的高速AD/DA模塊(集成PCIE接口和DDR3高速儲(chǔ)存單元)和工控機(jī)業(yè)務(wù)板分為發(fā)送端部分和接受端兩部分,板載一塊Xilinx公司V6系列FPGA進(jìn)行統(tǒng)一的系統(tǒng)邏輯控制和數(shù)據(jù)轉(zhuǎn)送轉(zhuǎn)換,。

發(fā)送端:

位于工控機(jī)中的PCIE接口主要負(fù)責(zé)將發(fā)送端用戶數(shù)據(jù)的發(fā)送到業(yè)務(wù)板的高速DAC上,,采用采用8xPCIE高速接口,大可以產(chǎn)生1.5GB的連續(xù)讀寫數(shù)據(jù)流

終在DAC輸出產(chǎn)生符號率為1024的模擬信號:

14bit高速DAC,,支持500MSPS的數(shù)據(jù)率,,1GHz的采樣時(shí)鐘驅(qū)動(dòng)。14bit位寬,,保障1024符號率的數(shù)據(jù)足夠的信噪比和無INL誤差,。

1、高板載4GB內(nèi)存,,PCIEx8接口,,支持1.5GB的連續(xù)數(shù)據(jù)傳輸速率

2、能實(shí)時(shí)并重復(fù)放送4G采樣點(diǎn)用戶數(shù)據(jù),。

3,、高速1GHzDAC時(shí)鐘產(chǎn)生和驅(qū)動(dòng),數(shù)據(jù)同步的時(shí)鐘與同步觸發(fā)信號輸出,。

4,、板載高速大規(guī)模FPGA,用戶可自定義邏輯,。

5,、高速信號放大輸出。

6,、可編程低抖動(dòng)時(shí)鐘發(fā)生器,。

接收端

同理,接受端也部署了相同的發(fā)端系統(tǒng)用于解調(diào)。同樣需要業(yè)務(wù)板上的高速DAC和PCIE高速接口傳輸數(shù)據(jù),。為采集光解調(diào)模塊輸出的4個(gè)相位的3電平信號,,我們在接收端業(yè)務(wù)版上安置了2塊雙通道高速ADC,采樣率為1GSPS,,8bit精度,。由于采樣數(shù)據(jù)只是3電平歸零碼(RZ),經(jīng)過轉(zhuǎn)換后變?yōu)?bit歸零碼(NRZ),,因此我們采用PCIE接口同步接受ADC的輸出數(shù)據(jù)就可以滿足帶寬和容量的需求了,。

框圖如下:需要配圖

系統(tǒng)各功能模塊描述:

高速DAC接口

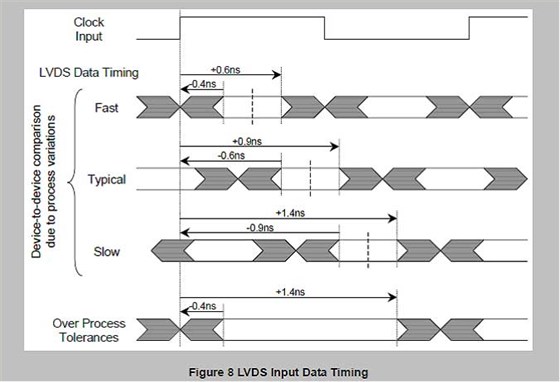

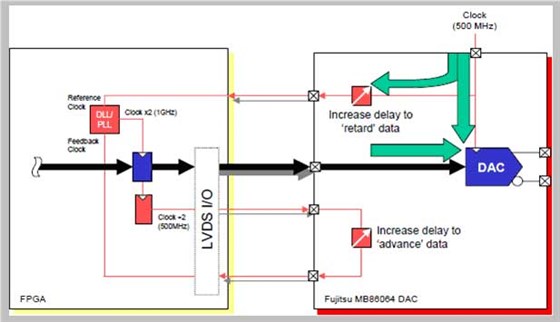

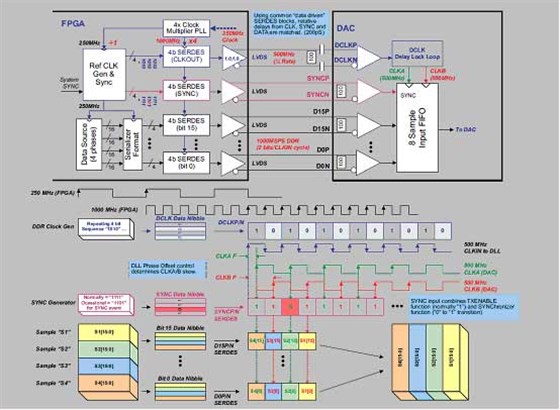

由于絕大多數(shù)FPGA芯片都無法工作在1GHz時(shí)鐘頻率下,我們選用的DAC芯片提供了雙通道LVDS接口,,將數(shù)據(jù)率減小到500MSPS,減小了FPGA設(shè)計(jì)難度和提高了系統(tǒng)的可靠性,。

DAC同F(xiàn)PGA的接口為LVDS

上圖所示,數(shù)據(jù)DDR形式,,數(shù)據(jù)的速率為時(shí)鐘的兩倍,。

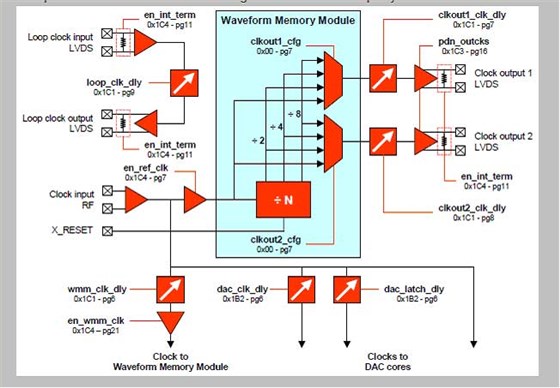

時(shí)鐘方案如下所示:

DAC的時(shí)鐘有著特殊的設(shè)計(jì),可以通過環(huán)回來抵消PCB的延遲,,從而更能可靠的傳輸數(shù)據(jù)。

1GHzSPSADC方案:

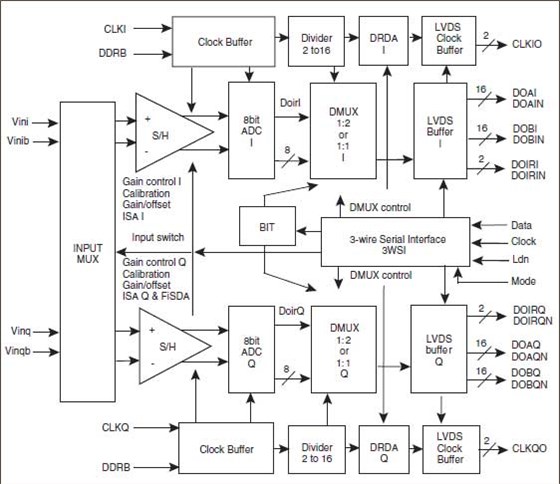

我們采用兩片Dual1GSPS8bitADC作為光解調(diào)信號的采集器,。

ADC的規(guī)格如下:需要配圖

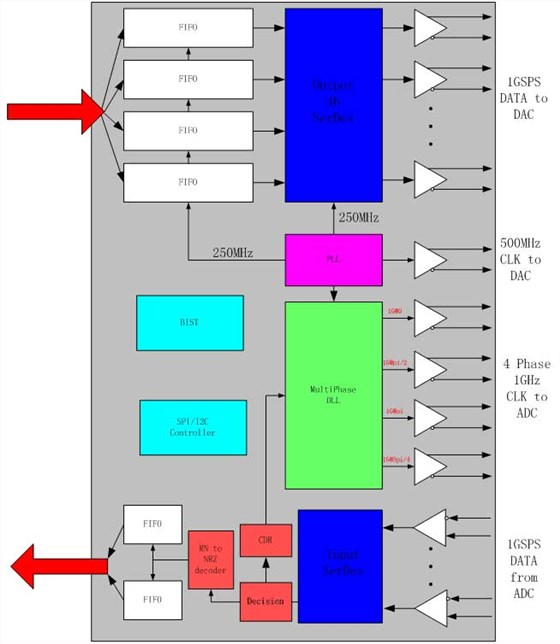

其框圖為:

系統(tǒng)中我們采用兩片DualADC組成4相位的時(shí)間交錯(cuò)采集系統(tǒng),,來分別采集光解調(diào)器輸出的4個(gè)不同相位的1GSPS歸零碼數(shù)據(jù)。

4.4FPGA邏輯方案:

FPGA整體方案如下所示:

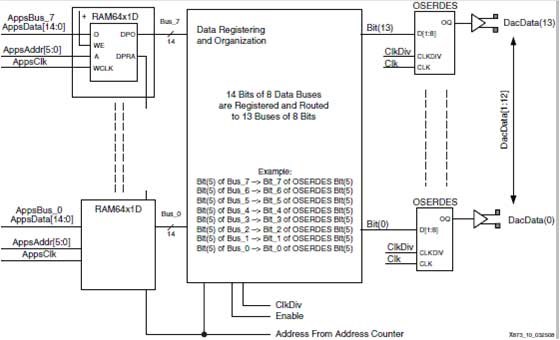

4.4.1發(fā)送端FPGA邏輯:

由于IP限制,,該模塊并不能支持3b(3倍頻串行)傳輸,,只能4b,8b等倍率傳輸,,這就限制了我們大利用數(shù)字板卡帶寬的想法,。只能采用如下方式進(jìn)行數(shù)據(jù)編組:每塊卡32bit編為兩組,高10位和低10位,;工作在125M下,,輸入到FPGA后合并為250M速率的10bit數(shù)據(jù)。系統(tǒng)共用4塊卡同時(shí)發(fā)送250M速率的10bit數(shù)據(jù),,我們就得到4個(gè)相位的數(shù)據(jù),,在FPGA中進(jìn)行串行化,終得到1G速率的10bit數(shù)據(jù),。

發(fā)送端的FPGA邏輯如下圖所示(14bitDAC):

輸入端需要加入同步FIFO進(jìn)行各通道數(shù)據(jù)的對齊,。

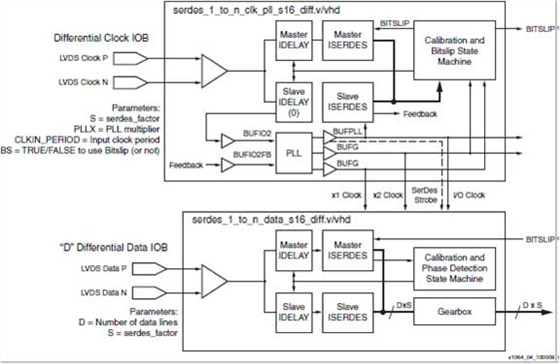

4.4.2接受端FPGA邏輯:

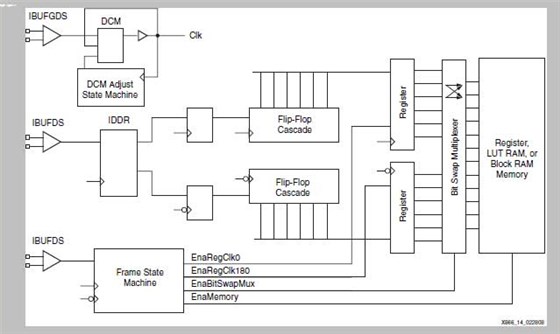

接收端要輸入1GSPS@8bit的數(shù)據(jù),同樣要使用到ISERDES模塊,,包括時(shí)鐘驅(qū)動(dòng)部分的邏輯如下圖所示:

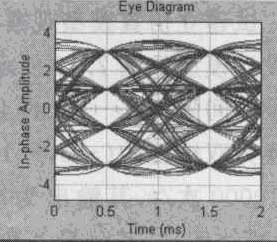

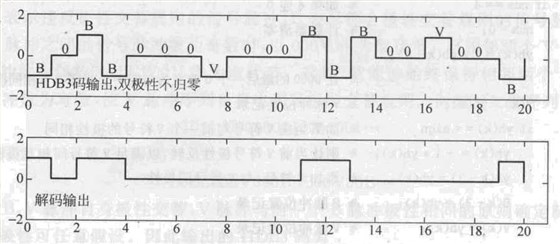

當(dāng)數(shù)據(jù)完成交錯(cuò)采集后,,進(jìn)入判決器模塊,判決器將8bit的模擬信號判決為歸零碼,再經(jīng)過歸零碼到非歸零碼解碼器進(jìn)行解碼:

輸出為1bitNRZ,,終輸出到PC中的數(shù)字IO卡中,。這樣大大降低了數(shù)據(jù)速率,同時(shí)數(shù)字板卡一次也能存儲(chǔ)更多的捕獲數(shù)據(jù),。

BIST(Buildinsystemtest)模塊方案:

BIST模塊通過產(chǎn)生或接受PRBSpattern和特定pattern,,來自動(dòng)測試整個(gè)數(shù)據(jù)傳送鏈路各個(gè)節(jié)點(diǎn)的工作情況,并能計(jì)算BER(誤碼率),。

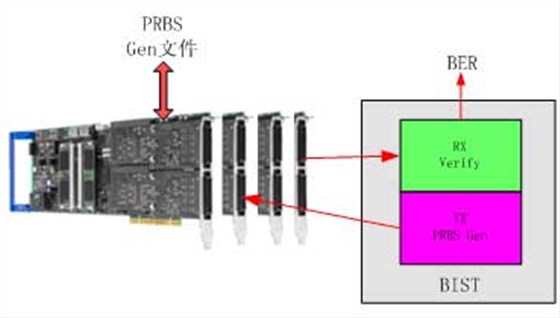

模式1:

校驗(yàn)數(shù)字IO卡輸入/輸出同F(xiàn)PGA間的鏈接通道,。

PRBS文件從PC經(jīng)過IO卡送入FPGABIST的RX模塊,進(jìn)行實(shí)時(shí)校驗(yàn),。

FPGABIST的TX模塊發(fā)送PRBSPattern,,經(jīng)過IO卡送入計(jì)算機(jī),在進(jìn)行PC上校驗(yàn)文件,。

BIST模式1

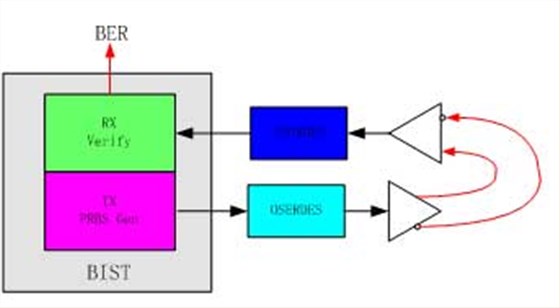

模式2:

ADC和DAC通道間的環(huán)回校驗(yàn),。主要檢測serdesTX端和RX端分別同DAC和ADC間的鏈接正確性。

BIST模式2

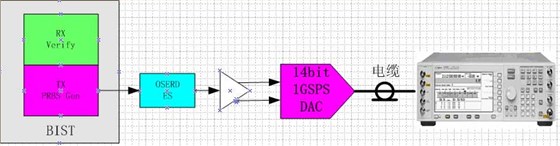

模式3:

發(fā)送端的校驗(yàn),,通過BIST模塊發(fā)送PRBS,,經(jīng)過serdes以及DAC,輸出NRZ或RZ碼,,接BERTEST儀器分析發(fā)送端的數(shù)據(jù)正確性,。

BIST模式3

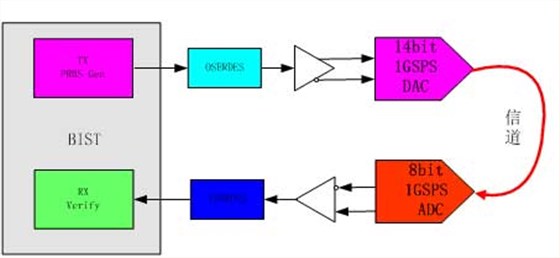

模式4:

整個(gè)鏈路的自環(huán)回校驗(yàn),可長時(shí)間計(jì)算BER,。

BIST模式4

系統(tǒng)實(shí)物圖和應(yīng)用環(huán)境:

同步收發(fā)模塊實(shí)物圖:

收發(fā)模塊同步工作實(shí)驗(yàn):

系統(tǒng)光路傳輸環(huán)境:

電話咨詢

電話咨詢 產(chǎn)品中心

產(chǎn)品中心 在線留言

在線留言 關(guān)于坤馳

關(guān)于坤馳