S波段收發(fā)信機方案設(shè)計

1,、收發(fā)信機功能

1)無線通信功能,通過天線發(fā)射已調(diào)制射頻信號,,通過天線接收調(diào)制信號,,并解調(diào)出信碼。

2)以FPGA+DSP通用硬件平臺,,實現(xiàn)多種調(diào)制信號產(chǎn)生算法驗證平臺,,如信道編碼、交織,、調(diào)制星座映射,、插值及濾波算法等。

3)以FPGA+DSP硬件平臺,,能夠完成多種解調(diào)算法驗證,,如載波同步、碼同步,、數(shù)字濾波等算法。

2,、收發(fā)信機技術(shù)指標

發(fā)信機

1)工作頻率:2.8GHz

2)輸出功率:-60-20dbm

3)功率控制步進:≤1dB

4)鄰道功率抑制:≥dB

5)調(diào)制制式:BPSK,、QPSK、QAM,、2FSK等

6)基帶碼速率:700Kbps

7)中頻:25MHz

8)帶寬:1.5MHz

9)本振輸出頻率:300MHz,、2475MHz

10)本振信號相噪:≤-96dBc/Hz@1k(2.8GHz)

11)本振信號雜散:≤-55dBc(非諧波)

收信機

1)射頻頻率:2.8GHz

2)接收靈敏度:≥-90dBm

3)功率動態(tài)范圍:90dB,自動增益控制

4)解調(diào)制式:BPSK、QPSK,、QAM,、2FSK等

5)中頻:25MHz

6)帶寬:1.5MHz

7)本振:300MHz、2475MHz

8)本振信號相噪:≤-100dBc/Hz@1k(1GHz)

9)本振信號雜散:≤-55dBc(非諧波)

10)中頻大輸出功率:≤5dBm

11)誤碼率:1×10-4(符號信噪比12dB)

3,、收發(fā)信機總體方案設(shè)計

3.1收發(fā)信機組成

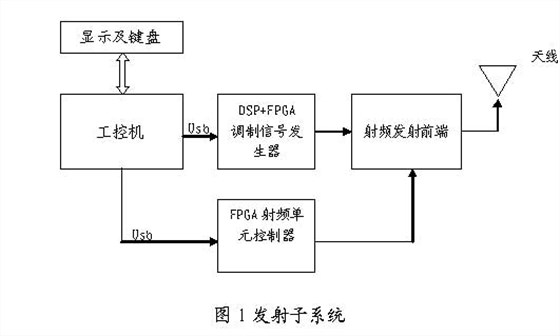

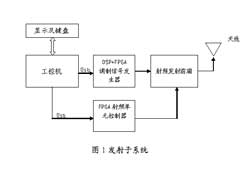

軟件無線電通信驗證系統(tǒng)主要包括發(fā)信機和收信機兩個子系統(tǒng),,由系統(tǒng)控制器,、系統(tǒng)顯示器鍵盤、DSP+FPGA調(diào)制信號發(fā)生器,、射頻發(fā)射前端,、發(fā)射天線組成發(fā)信機子系統(tǒng);由系統(tǒng)控制器,、系統(tǒng)顯示器鍵盤,、接收天線、射頻接收前端,、DSP+FPGA數(shù)字解調(diào)器組成收信機子系統(tǒng),,系統(tǒng)組成框圖如圖1、2所示:

圖1發(fā)射子系統(tǒng)

圖2接收子系統(tǒng)

3.2發(fā)射子系統(tǒng)設(shè)計

這里主要對發(fā)射子系統(tǒng)中關(guān)鍵模塊DSP+FPGA調(diào)制信號發(fā)生器,、射頻發(fā)射前端及控制進行設(shè)計說明,。

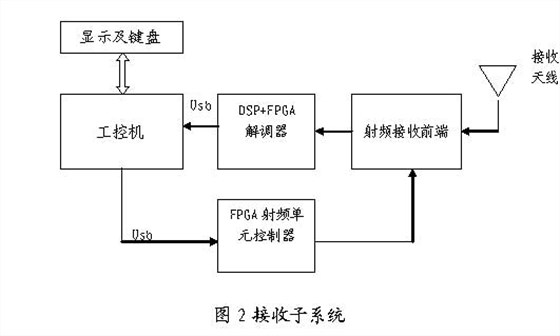

3.2.1 DSP+FPGA調(diào)制信號發(fā)生器

在統(tǒng)一的硬件平臺上,實現(xiàn)多種調(diào)制信號,,需采用軟件無線電設(shè)計思想,。調(diào)制信號發(fā)生器采用DSP+FPGA+DAC架構(gòu),具有很強的通用性和靈活性,,DSP通過USB接口接收用戶設(shè)置的調(diào)制方式,、調(diào)制碼速率等參數(shù),并解析工控機上層軟件指令,,配置FPGA內(nèi)濾波器和時鐘,,F(xiàn)PGA根據(jù)配置產(chǎn)生相應(yīng)的調(diào)制映射、濾波器,、數(shù)字載波等,,終生成數(shù)字中頻信號,再通過DAC,,輸出模擬中頻信號,。原理框圖如圖3所示。

圖3

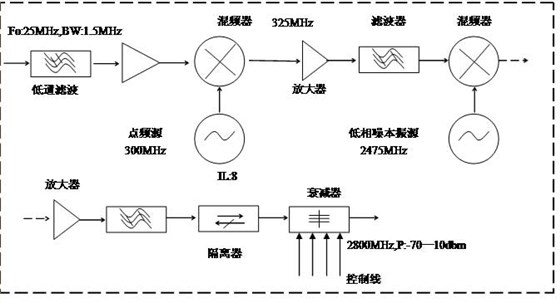

3.2.2 射頻發(fā)射前端

射頻發(fā)射模塊采用二次上變頻設(shè)計完成對中頻信號的變頻處理和發(fā)射,。發(fā)射模塊主要由中頻低通濾波器,、上變頻器、放大器,、大動態(tài)/小步進功率衰減器,、檢波器組成,見圖4。

圖4

其中,,300MHz點頻源采用直接倍頻,、濾波方法產(chǎn)生,將系統(tǒng)時鐘100MHz通過寬帶放大器飽和放大產(chǎn)生,,100MHz的N次諧波,,再通過濾波器取出3次諧波300MHz,。

2475MHz點頻源采用鎖相環(huán)PE3336實現(xiàn),實現(xiàn)原理框圖如圖5所示,。

圖5

3.3接收子系統(tǒng)設(shè)計

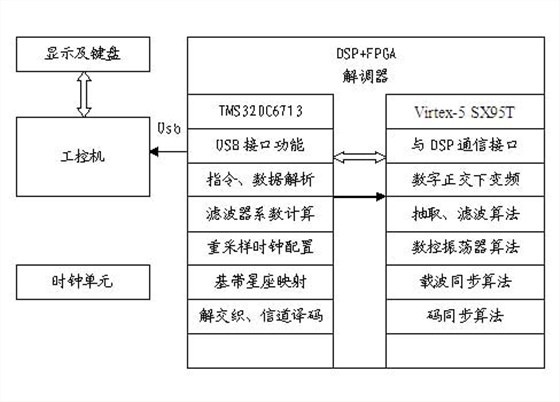

3.3.1 DSP+FPGA數(shù)字解調(diào)器

為了實現(xiàn)多種調(diào)制制式的解調(diào),,采用ADC+FPGA+DSP的硬件架構(gòu),ADC以帶通過采樣方式采集中頻信號,,采集后數(shù)字中頻信號在FPGA內(nèi)實現(xiàn)抽取,、濾波、載波同步,、碼同步數(shù)字信號處理,,處理后在DSP內(nèi)實現(xiàn)解調(diào)、解交織,、解碼,,終碼數(shù)據(jù)通過USB上傳至工控機,進行比對分析,、星座圖顯示等,。原理框圖如圖6所示。

圖6

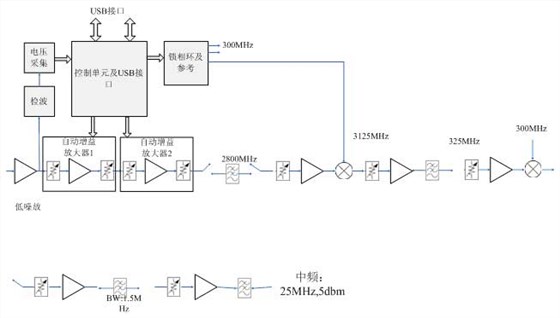

3.3.2 射頻接收前端及控制

射頻接收前端主要由低噪聲放大器,、鏡像濾波器,、自動增益放大器、射頻檢波電路,、開關(guān),、混頻器、本振源等電路組成,。射頻接收前端原理框圖如圖7所示,。射頻接收前端低噪聲放大器增加射頻接收前端靈敏度,功率檢波電路測量低噪聲放大器輸出的射頻信號功率,,控制自動增益放大器滿足射頻接收前端-90—10dbm線性功率動態(tài)范圍的要求,,并使得射頻輸入電平處于混頻器、中頻放大器及檢波器的佳量程范圍,。

圖7

3125MHz點頻源采用鎖相環(huán)ADF4350實現(xiàn),。

電話咨詢

電話咨詢 產(chǎn)品中心

產(chǎn)品中心 在線留言

在線留言 關(guān)于坤馳

關(guān)于坤馳