系統(tǒng)規(guī)格:

系統(tǒng)采用緊湊的PCIe架構(gòu),,包括如下幾個(gè)部分:

1.PCIE DAC直接RF頻率合成信號(hào)產(chǎn)生模塊QT2135+QTF-257B:

l2通道14bit 5.6GSPS同步采集模塊,。

l50歐姆AC,、DC耦合,,輸出滿幅度500mVpp。

l支持IQ雙通道基帶信號(hào)輸出,,模擬輸出帶寬DC~1GHz,。

2.直接RF頻率合成信號(hào)產(chǎn)生模塊QTF-6120

l寬帶IQ信號(hào)輸入

l支持基帶輸入帶寬1GHz

lRF混頻模式輸出

l帶寬2GHz~4.2GHz

l自帶LO功能

3.高速存儲(chǔ)板QT-C3000:

l500GB 存儲(chǔ)容量。

l高速FLASH SSD陣列,,支持大2GB/s的連續(xù)讀寫(xiě)速率,。

lPCIex8接口,支持DMA傳輸,。

l通過(guò)高速PCIE總線DA板連接,,傳輸帶寬大于2GB/s。

4.時(shí)鐘模塊SC5506A:

l直接驅(qū)動(dòng)射頻DAC轉(zhuǎn)換時(shí)鐘,。

l輸出頻率100MHz~6GHz,。

l相位噪聲<-117dBc/Hz at 10KHz。

l時(shí)鐘調(diào)節(jié)精度1Hz,。

l輸出功率:大13dBm,。

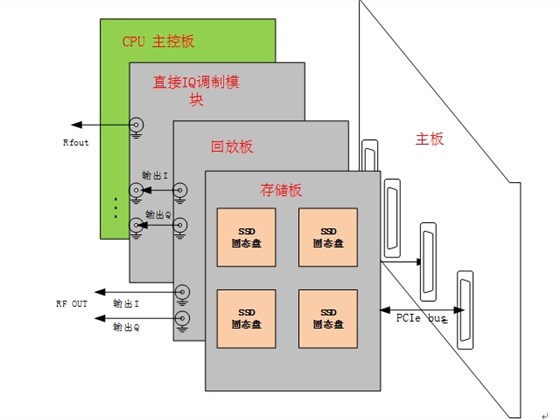

大容量直接RF頻率合成信號(hào)產(chǎn)生系統(tǒng)實(shí)現(xiàn)方案:

整個(gè)系統(tǒng)由高速DAC卡產(chǎn)生IQ基帶信號(hào)、帶LO功能的直接IQ調(diào)制發(fā)生模塊輸出RF信號(hào),、高速大容量SSD存儲(chǔ)卡用于存儲(chǔ)基帶信號(hào)數(shù)據(jù)以及PCe工作站組成,。

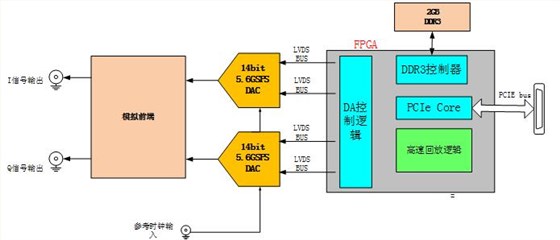

寬帶基帶信號(hào)發(fā)生高速DAC卡

DAC模塊外觀如下:

DAC模塊原理和性能

基于PCIe的DAC回放卡整體原理框圖

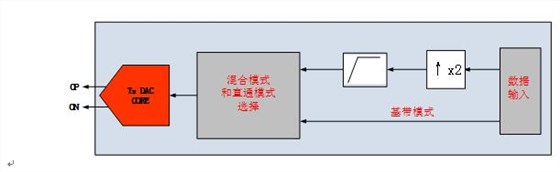

DAC工作原理圖

直接RF頻率合成DAC支持基帶模式和混合模式:

l基帶模式,直接RF高支持LF~1GHz帶寬,,大DAC更新率為2.85Gsps,,可采用插值2倍輸出,及數(shù)字時(shí)鐘更新率高到5.7Gsps,,減小1G內(nèi)的帶寬sinc衰減,;

并支持兩通道同步輸出基帶IQ信號(hào)。

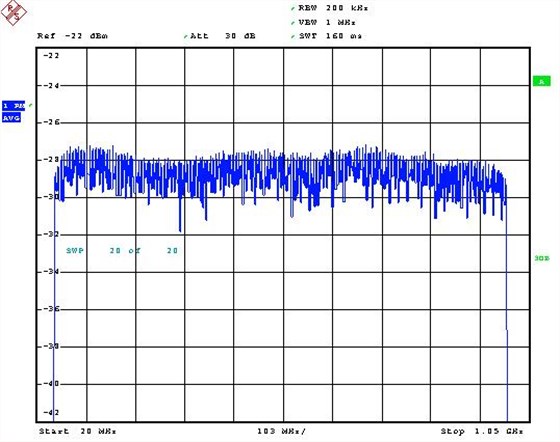

基帶模式下的帶寬測(cè)試結(jié)果:

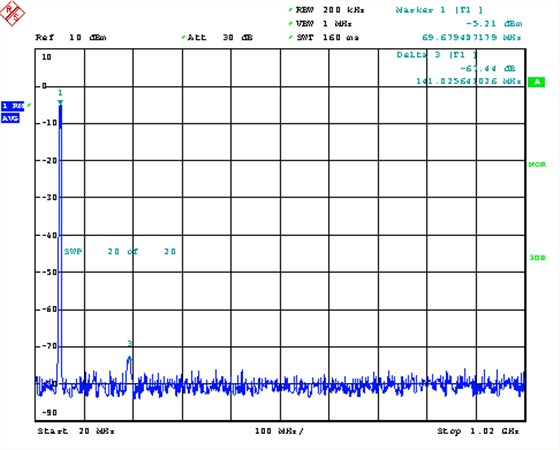

基帶模式下的SFDR測(cè)試結(jié)果:

直接IQ調(diào)制模塊

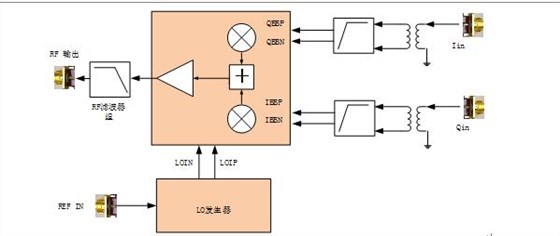

IQ混頻器原理框圖

·

混頻模式下寬帶正交調(diào)制器性能指標(biāo):

lLO輸入大頻率:6GHz,。

l基帶IQ輸入帶寬BW:DC~1GHz,。

l諧波失真:2次諧波小于-60dBc;3次諧波小于-59dBc,;

RF out在3300MHz,。

LO輸出指標(biāo)

l輸出頻率100MHz~6GHz。

l相位噪聲<-117dBc/Hz at10KHz,,-140dBc/Hz at 1MHz,,

l時(shí)鐘調(diào)節(jié)精度1Hz。

l輸出功率:10dBm大,。

電話咨詢

電話咨詢 產(chǎn)品中心

產(chǎn)品中心 在線留言

在線留言 關(guān)于坤馳

關(guān)于坤馳