1.硬件要求:

兩通道輸入,,信號(hào)輸入為0-5V數(shù)字信號(hào),。

FPGA主板采用單片xilinxV6FPGA,支持xc6vlx240t-lff1156,,兼容xc6vlx130t-lff1156,。

板載FLASH配置FPGA,通過JTAG配置FPGA,。

數(shù)據(jù)由RS232輸出,。

信號(hào)輸入端口帶6VBreakdown電壓ESD保護(hù),。

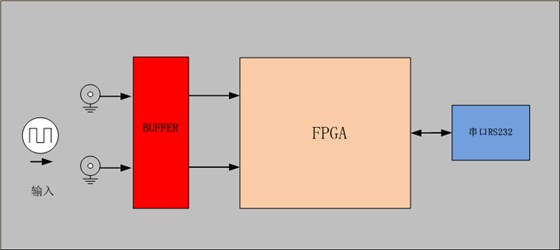

2.系統(tǒng)原理

整個(gè)系統(tǒng)采用子母卡形式,采集子板通過buffer采集數(shù)字信號(hào),,然后由主板FPGA做邏輯算法,,終由載板通過RS232輸出檢測(cè)數(shù)據(jù)。

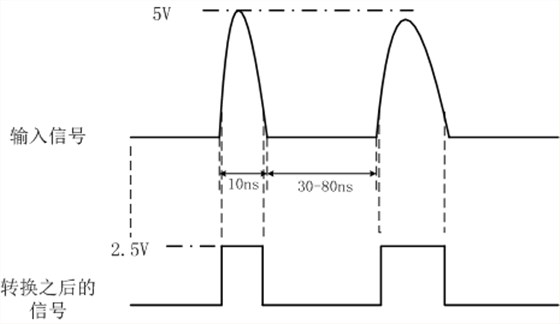

信號(hào)輸入為5VTTL電平或者脈沖,,需要轉(zhuǎn)換成,,可選擇兩種方案:

①5VTTL轉(zhuǎn)2.5V,可采用電平轉(zhuǎn)換驅(qū)動(dòng)器或者CPLD,。5V轉(zhuǎn)2.5V的buffer,,可選用TI的SN74LVC2T45(140Mbps),CPLD可選用XILINX的XC9500XL系列的XC9536XL-7VQ44C,。如下圖:

②5VTTL轉(zhuǎn)LVDS,,采用TTL轉(zhuǎn)LVDS芯片,可選用TI的四路DS90C032TM(>155.5Mbps)或者M(jìn)AXIM的單路MAX9164(200Mbps),。

電話咨詢

電話咨詢 產(chǎn)品中心

產(chǎn)品中心 在線留言

在線留言 關(guān)于坤馳

關(guān)于坤馳