基于PCIe總線的多通道采集回放系統(tǒng)可實(shí)現(xiàn)高速信號(hào)的采集、存儲(chǔ)及快速回放功能,,坤馳科技的系統(tǒng)具備PCIe總線的快速數(shù)據(jù)傳輸能力,、ADQ14、CSE126G1系列板卡的高速高精度數(shù)據(jù)采集能力,、AWG2500系列任意波形發(fā)生器的快速數(shù)據(jù)回放能力,可實(shí)現(xiàn)單通道,、12bit,、6GS/s采樣率采集,;同時(shí),、可4通道,、輸入增益可調(diào),、14bit,、1GS/s采樣率采集,;高速采集的同時(shí)可實(shí)現(xiàn)2通道、14bit,、2.5GS/s 的任意波形回放,。

系統(tǒng)組成如下圖:

系統(tǒng)詳細(xì)介紹:

系統(tǒng)硬件包括用戶自選的PCIe總線的工控機(jī)箱,;一款型號(hào)為ADQ14DC-4C-VG的4通道、14bit,、1GS/s,可變輸入增益、2GB內(nèi)存的PCIe高速數(shù)據(jù)采集卡,;一款型號(hào)為CSE126G1的1通道、12bit,、6GS/s,、4GB內(nèi)存的PCIe高速數(shù)據(jù)采集卡,;一款型號(hào)為AWG2500-64M的2通道、14bit,、2.5GS/s,、64Msamples板上內(nèi)存的任意波形發(fā)生器,。

系統(tǒng)模塊介紹:

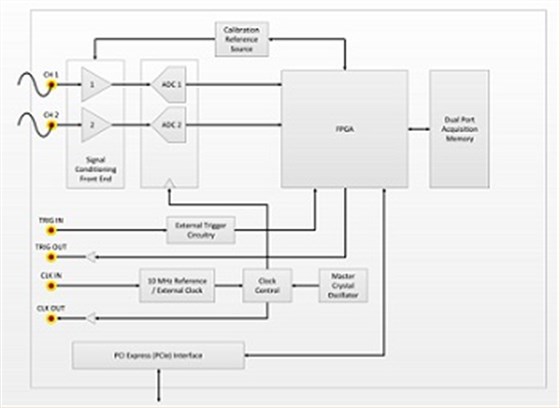

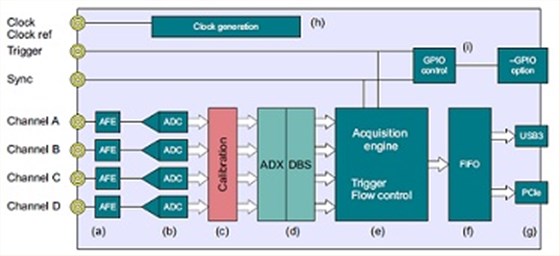

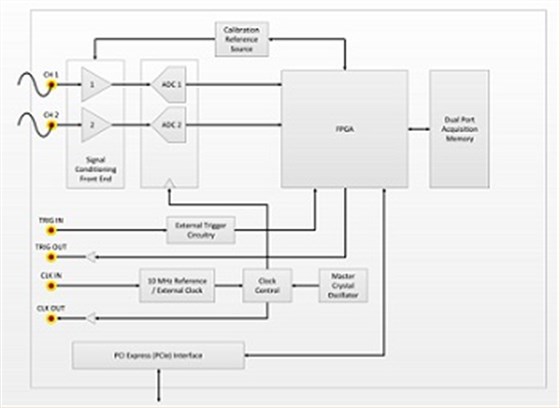

1),、ADQ14DC-4C-VG

規(guī)格:4通道,,1GS/s,14bit,DC耦合

接口形式:PCIe

輸入范圍:(VG):0.5, 1, 2, 5 Vpp

連接器:SMA

-3dB帶寬:700MHz

時(shí)鐘:內(nèi)/外時(shí)鐘參考

觸發(fā):軟件、內(nèi)部觸發(fā),、外觸發(fā)輸入/輸出,、電平觸發(fā)

其他:雙槽,、支持GPIO,、過壓保護(hù)

FPGA:Xilinx Kintex 7 K325T,、支持用戶二次開發(fā)

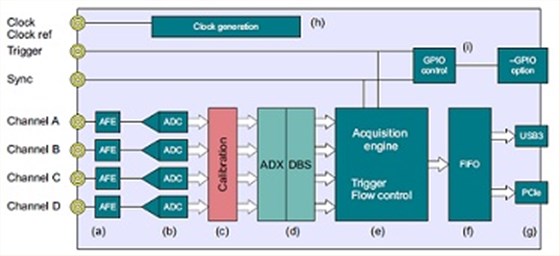

A),、板卡架構(gòu)圖

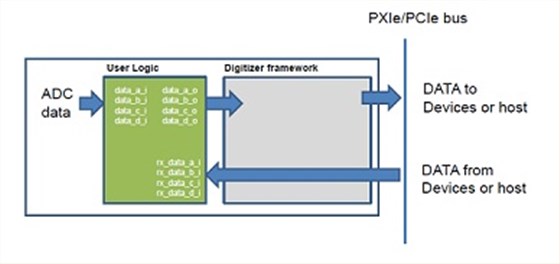

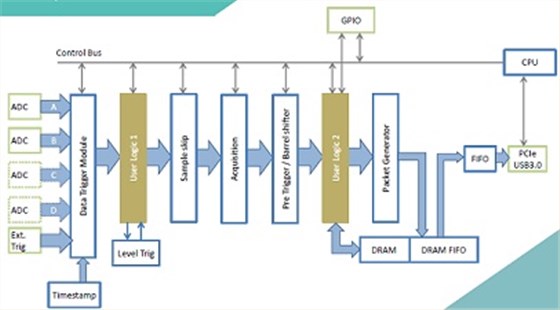

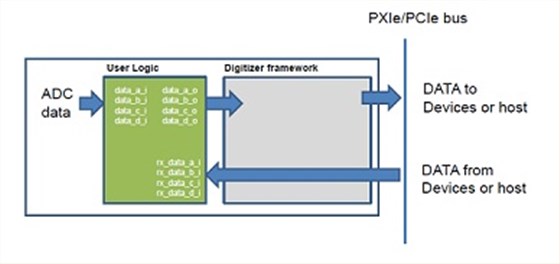

B),、數(shù)據(jù)流控制

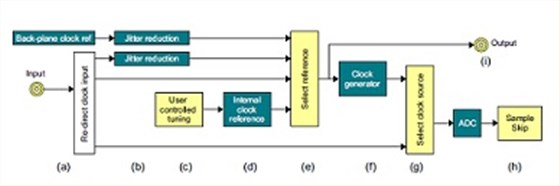

C),、時(shí)鐘控制

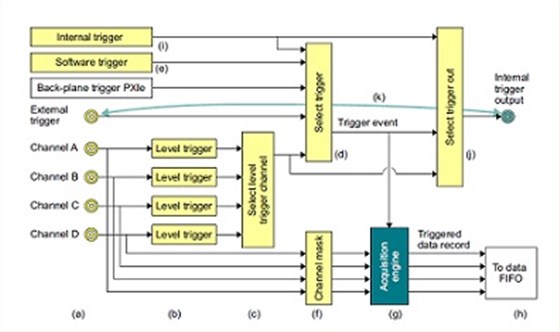

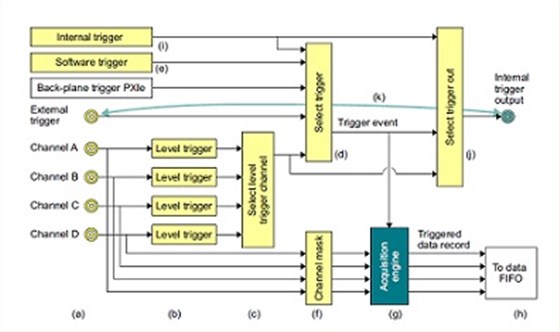

D)、觸發(fā)設(shè)置

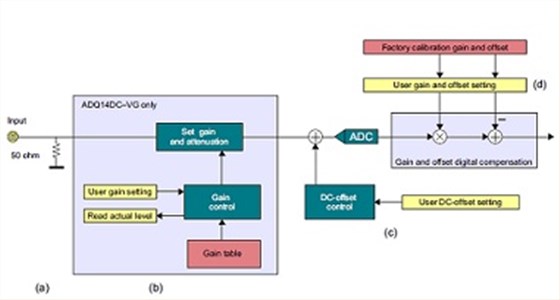

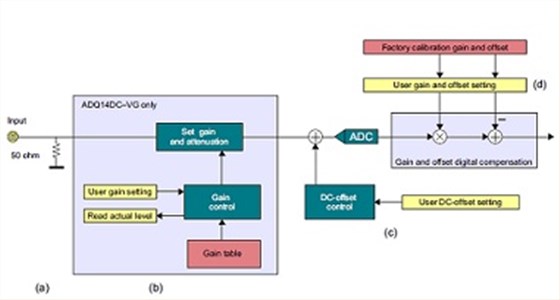

E),、模擬前端AFE設(shè)置

F),、觸發(fā)模式

數(shù)據(jù)流模式(triggered streaming)-適合大化的利用數(shù)據(jù)傳輸?shù)街鳈C(jī)的速度

多段記錄模式(multi record mode)-適合大量數(shù)據(jù)的實(shí)時(shí)采集

G)、采集控制設(shè)置

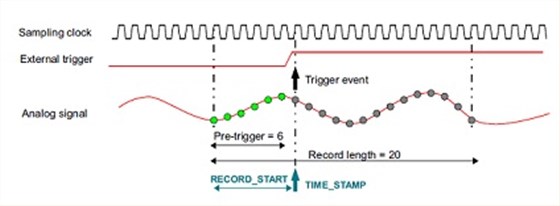

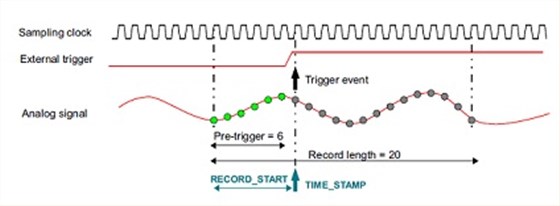

·Pre-trigger模式

注:數(shù)據(jù)流模式(streaming mode)下,,預(yù)觸發(fā)的長度是有限的,,對比之下,,多段記錄模式下(multi-record)高可達(dá)234個(gè)采樣點(diǎn),。

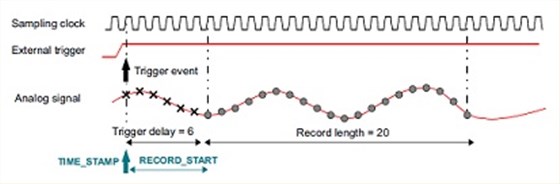

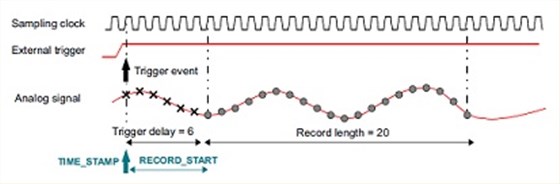

·Hold-off (Delay)模式

•延遲長度高可達(dá)234個(gè)采樣點(diǎn)(取決于板卡模式)

H)、用戶FPGA二次開發(fā)選項(xiàng)

SDK提供一些開發(fā)平臺(tái)的編程實(shí)例和參考工程,ADQAPI 參考指導(dǎo)詳細(xì)的描述了所有功能,,很多例子和應(yīng)用筆記會(huì)有助于用戶開發(fā),。使用SDK可幫助用戶實(shí)現(xiàn)數(shù)字化儀的大量數(shù)據(jù)處理和實(shí)時(shí)控制。

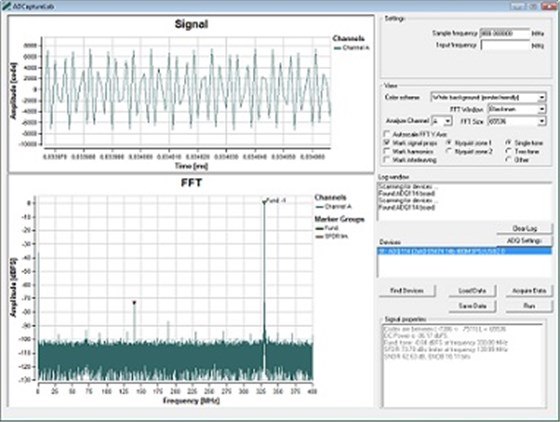

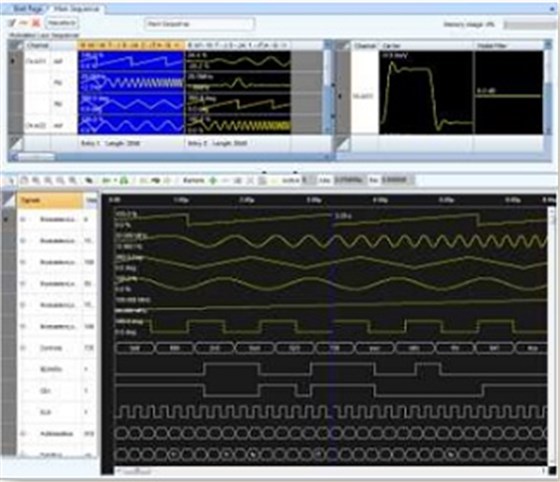

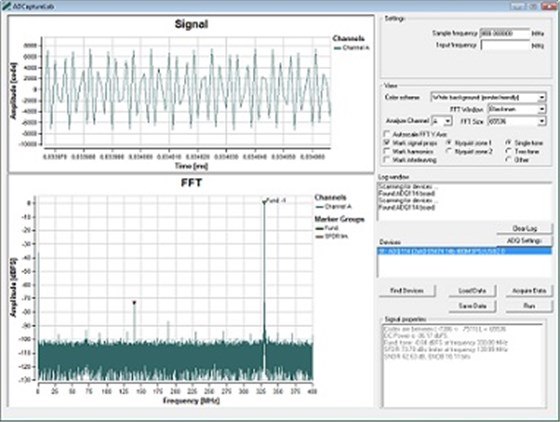

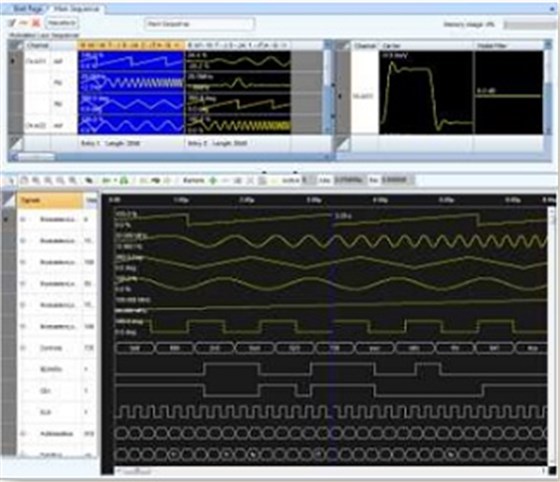

J),、板卡軟件界面

•UI界面:ADCapture Lab

•C/Matlab/Python 采集例程可用

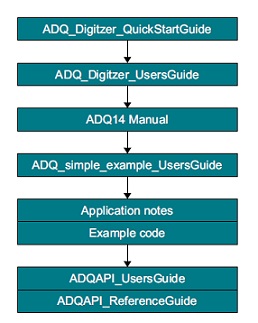

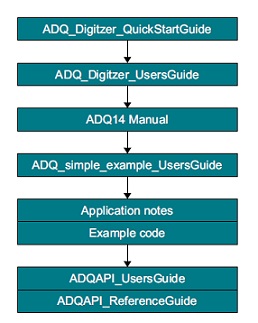

•ADCapture Lab安裝后,,安裝目錄生成以下豐富參考文件及API.

2)、CSE126G1

規(guī)格:1通道,,6GS/s,12bit,DC耦合

接口形式:PCIe

輸入阻抗:50?

輸入范圍:±100 mV, ±200 mV, ±500 mV,

±1 V, ±2 V, ±5 V(軟件選擇)

輸入調(diào)節(jié):直流偏置(輸入范圍內(nèi))

過壓保護(hù):±6 V

連接器:SMA

-3dB帶寬:1.75GHz

板上內(nèi)存:4GB

時(shí)鐘:內(nèi)/外時(shí)鐘參考

觸發(fā):外觸發(fā)輸入/輸出,、電平觸發(fā)

同步:可設(shè)置為多通道同步主/從模式

大傳輸率:4GB/s

FPGA:SDK開發(fā)包支持C/C#, LabVIEW ,MATLAB

操作界面:GaGeScope PC 示波軟件

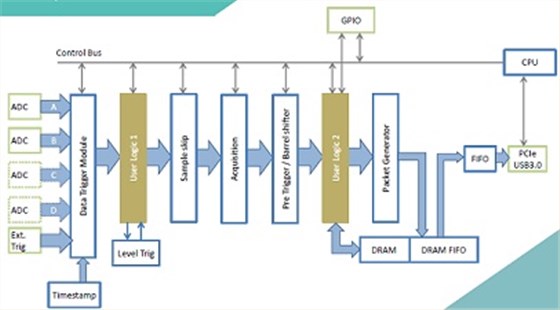

A)、板卡框圖:

B),、觸發(fā)

觸發(fā)源:通道觸發(fā),、外部觸發(fā)、軟件觸發(fā)

組合觸發(fā):所有觸發(fā)方式以“或(OR)”邏輯組合使用

觸發(fā)信號(hào)要求:上升沿或下降沿(軟件選擇)

靈敏度:滿量程觸發(fā)源輸入范圍的±5%

C),、外部觸發(fā)

連接器:SMA

匹配阻抗:1K ?

耦合方式:AC

帶寬:>100MHz

電壓范圍:0-3V(非極性)

D)、觸發(fā)輸出

連接器:SMA

匹配阻抗:50 ?

幅度:0-TTL

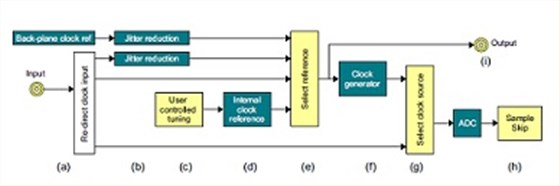

E),、時(shí)鐘輸入

連接器:SMA

電壓:小0.2V RMS,大0.5RMS

匹配阻抗:50 ?

耦合方式:DC

占空比:50% ±5%

輸入模式:外部時(shí)鐘或10MHz時(shí)鐘參考

F)、時(shí)鐘輸出

連接器:SMA

電壓:0-1.5V

匹配阻抗:50 ?

占空比:50%

輸出模式:半采樣時(shí)鐘頻率或10MHz時(shí)鐘參考

采樣時(shí)鐘:小 200MHz

模式速率:大3GHz

10MHz參考:10MHz(來自于外部時(shí)鐘)

G)、多段模式

預(yù)觸發(fā)長度:大為FPGA內(nèi)存大小

H),、多卡系統(tǒng)

主/從(Master/Slave)模式:多通道系統(tǒng)的所有板卡的所有通道

獨(dú)立模式:系統(tǒng)內(nèi)每個(gè)板卡獨(dú)立操作

J)、PC系統(tǒng)需求

PCIe插槽:1個(gè)全長PCIe gen1,gen2或gen3,x8或x16插槽

操作系統(tǒng):Windows 7(32-bit/64-bit)

Windows 8 (32-bit/64-bit)

Linux – Requires SDK for C/C#

K)、其他指標(biāo)

尺寸:單槽,,全高、3/4 長

電源功耗:25W

3)、AWG2500-64M 任意波形發(fā)生器

規(guī)格:2通道,,2.5GS/s,14bit

-3dB帶寬:1GHz

DAC直接輸出-DC耦合:1.6 Vpp 差分/ 0.8 Vpp 單端.

RF放大輸出-AC耦合:-10 dBm to +10 dBm 差分輸出

板上內(nèi)存:64M/每通道

諧波失真:<-65 dBc

非諧波失真:<-74dBc (1kHz to 1GHz)

多通道同步:10ps分辨率控制

數(shù)字模式發(fā)生器:16/32 Bits @ 1250/625 Mbps

其他:任意,、DDS和功能發(fā)生模式,先進(jìn)的波形序列發(fā)生器

A)、特點(diǎn):

RF信號(hào)發(fā)生功能

數(shù)字化模塊設(shè)計(jì)

非常低的諧波失真

輸出選擇:RF放大,,直接DAC輸出,、

DC放大

高速數(shù)字化輸出

多個(gè)設(shè)備同步

任意、DDS和功能發(fā)生模式

B),、用戶操作軟件

功能易用操作軟件

先進(jìn)的任意(Arbitrary)/DDS 操作界面

帶有環(huán)路,,條件跳變和子序列功能的強(qiáng)大序列發(fā)生器

電話咨詢

電話咨詢 產(chǎn)品中心

產(chǎn)品中心 在線留言

在線留言 關(guān)于坤馳

關(guān)于坤馳