1系統(tǒng)采用標(biāo)準(zhǔn)的3U PXIe架構(gòu),包括如下幾個(gè)部分:

1.板載高速存儲(chǔ)器,每通道支持512Msamples采樣點(diǎn)存儲(chǔ),。

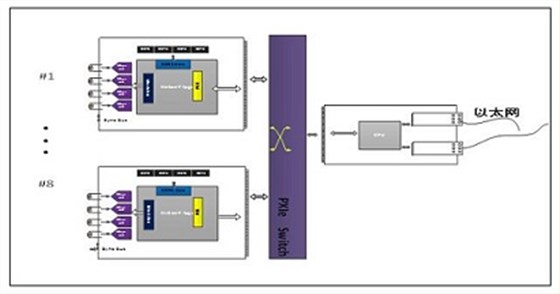

3.標(biāo)準(zhǔn)3U 18槽系統(tǒng),,包括3U 18槽背板,控制器以及機(jī)箱,,控制器模塊可以通過(guò)以太網(wǎng)口將各通道的采集數(shù)據(jù)傳輸?shù)缴衔粰C(jī)進(jìn)行數(shù)據(jù)處理,。

5.上位主控計(jì)算機(jī),通過(guò)千兆以太網(wǎng)控制各個(gè)采集系統(tǒng),,并從采集系統(tǒng)中讀取每通道的采集數(shù)據(jù),。

采用標(biāo)準(zhǔn)3U PXIe機(jī)箱,整個(gè)系統(tǒng)緊湊,,符合工業(yè)級(jí)溫度工作范圍,,-40C°至85C°。

2.每個(gè)機(jī)箱采用獨(dú)立的時(shí)鐘/觸發(fā)控制模塊,,進(jìn)行時(shí)鐘和觸發(fā)信號(hào)的分發(fā),,采用星形拓?fù)浣Y(jié)構(gòu),通過(guò)背板的高速互連線進(jìn)行等延遲的統(tǒng)一分發(fā)時(shí)鐘和觸發(fā)信號(hào),。

4.通過(guò)自定義背板連接信號(hào),,增加了系統(tǒng)的緊湊性,大量減少了連接線。

系統(tǒng)實(shí)現(xiàn)框圖如下:

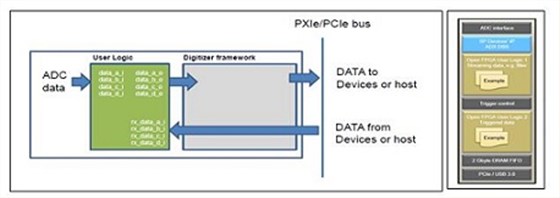

數(shù)據(jù)傳輸原理圖:

2利用卓越的多單元同步方案可搭建集成多系列,、大量檢測(cè)器的同步系統(tǒng),,每塊ADQ14板卡都有一個(gè)同步輸入和同步輸出接口,所有的板卡可通過(guò)相關(guān)的操作鎖相到外部時(shí)鐘,。

采集模塊介紹

8通道500MSPS 14bit ADC,。

輸入阻抗:50 藕合/SMA

版本:0.5、2時(shí)鐘:支持板載時(shí)鐘或外時(shí)鐘

已開(kāi)發(fā)固件:累加,、脈沖檢測(cè),、軟件無(wú)線電等

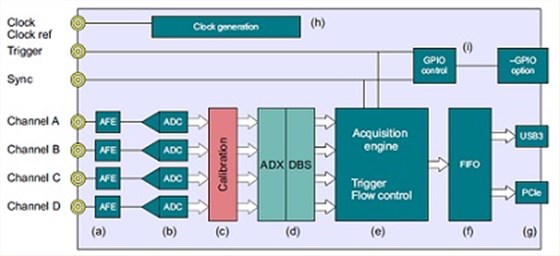

采集模塊的實(shí)現(xiàn)原理如下:

硬件模塊控制:

a),,時(shí)鐘模塊

,,觸發(fā)選項(xiàng)

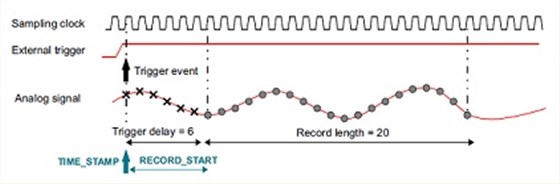

觸發(fā)模式

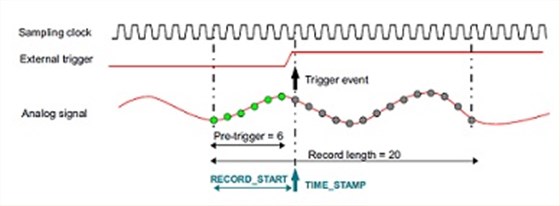

觸發(fā)的數(shù)據(jù)流模式(triggered streaming適合大化的利用數(shù)據(jù)傳輸?shù)街鳈C(jī)的速度

多段記錄模式(multi record mode適合大量數(shù)據(jù)的實(shí)時(shí)采集

e),,、 Pre-trigger

)下,預(yù)觸發(fā)的長(zhǎng)度是有限的,,對(duì)比之下,,多段記錄模式下(multi-record個(gè)采樣點(diǎn)。

2,、Hold-off (Delay)

個(gè)采樣點(diǎn)(取決于板卡模式)

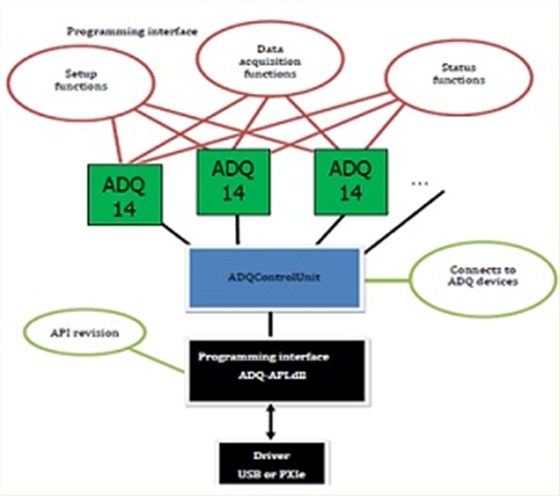

f),提供一些開(kāi)發(fā)平臺(tái)的編程實(shí)例和參考工程,,ADQAPI 可幫助用戶實(shí)現(xiàn)數(shù)字化儀的大量數(shù)據(jù)處理和實(shí)時(shí)控制。

4靈活的功能選項(xiàng):

板卡原理框圖:

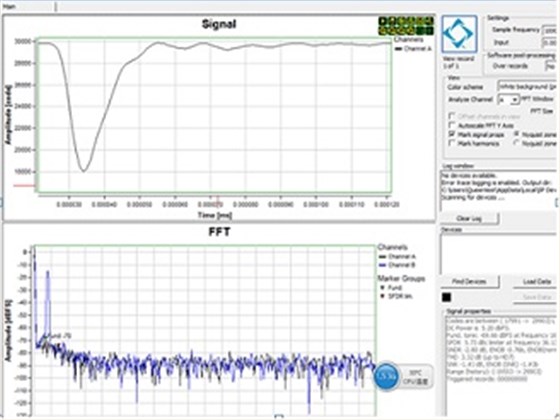

系統(tǒng)配套軟件

系統(tǒng)軟件包括應(yīng)用軟件,,二次開(kāi)發(fā)API函數(shù),。應(yīng)用軟件,具有虛擬示波器功能,,方便設(shè)置硬件,,讀取/保存數(shù)據(jù)以及波形顯示/頻譜分析功能。

1,、其功能和界面如下所示:

2,、二次開(kāi)發(fā)API函數(shù):

我們提供豐富的接口函數(shù)和系統(tǒng)主要功能的例程,支持C/C++,,labview以及Matlab環(huán)境下的二次程序開(kāi)發(fā),。

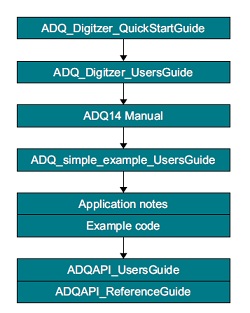

3、可提供指示文檔:

電話咨詢

電話咨詢 產(chǎn)品中心

產(chǎn)品中心 在線留言

在線留言 關(guān)于坤馳

關(guān)于坤馳